【導讀】精密數(shù)據(jù)采集的市場空間中存在一個普遍需求,即在保持性能的同時提高信號鏈的密度。由于越來越多的應用逐漸傾向于依照通道的ADC方式,或試圖將更多通道集成于同一尺寸中,因此通道密度是許多數(shù)據(jù)采集信號鏈設計工程師十分關(guān)注的問題。

此外,目前行業(yè)中存在的一個趨勢是,力求使精密電路更易于使用,并且能夠更輕松地實現(xiàn)數(shù)據(jù)手冊中的性能。這樣就有利于構(gòu)建一些子系統(tǒng),通過使用系統(tǒng)級封裝 (SiP) 技術(shù)實現(xiàn)信號鏈而解決上述問題。

ADI公司根據(jù)此子系統(tǒng)策略生產(chǎn)的第一個系列為ADAQ798x數(shù)據(jù)采集產(chǎn)品。ADAQ798x是一種16位模數(shù)轉(zhuǎn)換器子系統(tǒng),將四個通用的信號處理和調(diào)理模塊集成到一個SiP設計中,可支持多種應用。該系列器件也包含最關(guān)鍵的無源器件,可避免因使用逐次逼近型寄存器 (SAR) 模數(shù)轉(zhuǎn)換器 (ADC) 的傳統(tǒng)信號鏈所導致的很多設計難題。這些無源器件是實現(xiàn)額定器件性能的關(guān)鍵因素。

縱觀使用SAR ADC的應用和市場,如工業(yè)、儀器儀表、通信及醫(yī)療保健,可以發(fā)現(xiàn),數(shù)據(jù)采集信號鏈的某些部分在這些應用中很常見,而另外某些部分則可能存在廣泛的不同。還可以發(fā)現(xiàn),這些信號鏈使用不同的輸入源和傳感器陣列。因此,在向ADC提交信號之前,將會執(zhí)行各種形式的信號調(diào)理。使用不同的輸入源意味著系統(tǒng)的滿量程可能不同,并且需要采用不同的基準值以使動態(tài)范圍最大化。某些應用為多通道方式,因此會使用一個前端多路復用器。根據(jù)不同應用的關(guān)鍵性能標準,可能會實施不同的供電方案。不過,無論何種應用,某些器件可通用于很多場合。ADAQ7980 和 ADAQ7988 是全ADI有源器件解決方案的組成部分,該解決方案包含一個高精度、低功耗的16位SAR ADC;一個低功耗、高帶寬、高輸入阻抗的ADC驅(qū)動器;一個穩(wěn)定的低功耗基準電壓緩沖器;以及一個高效的電源管理模塊。這些信號鏈組件已通過SiP技術(shù)集成到一個數(shù)據(jù)采集子系統(tǒng)中。

ADAQ7980和ADAQ7988均采用小尺寸5 mm × 4 mm LGA封裝,因此會使數(shù)據(jù)采集系統(tǒng)的設計過程更簡單。ADAQ798x的高系統(tǒng)集成度可解決很多設計難題,并且仍具有靈活性,能夠通過可配置的ADC驅(qū)動器模塊實現(xiàn)增益和/或共模調(diào)整。配備四種器件電源以提供最佳系統(tǒng)性能,但在對器件工作特性的影響極小時也可使用單電源模式。ADAQ798x系列不僅具有出色的集成度,并且可靈活地適應各種各樣的應用。

AD I公司在開發(fā)此產(chǎn)品時對常見的設計錯誤進行了分析,以確定出有助于解決這些問題的方法。結(jié)果表明,信號鏈層設計中的很多錯誤主要圍繞 SAR ADC的兩個區(qū)域—參考輸入和模擬輸入。很多信號鏈誤差都與決定整體模數(shù)轉(zhuǎn)換性能的ADC的外圍電路有關(guān)。關(guān)于基準電壓,常見的錯誤包括基準旁路電容的布局和尺寸不當,基準電壓源的驅(qū)動強度不足,以及基準電壓源產(chǎn)生的噪聲頻譜密度過大。若SAR ADC的參考輸入存在這些不妥當?shù)脑O計條件,可能會導致ADC作出錯誤的位判斷。至于ADC的模擬輸入,觀察到的常見設計問題包括:ADC驅(qū)動器選型不當,ADC驅(qū)動器和ADC之間濾波器的帶寬不適當,以及濾波電容介電材料選擇不當。這些系統(tǒng)級設計問題以任何方式組合都可能會嚴重影響ADC的轉(zhuǎn)換性能。ADI公司在開發(fā)ADAQ798x器件時所作的一系列選擇都旨在解決這些問題。

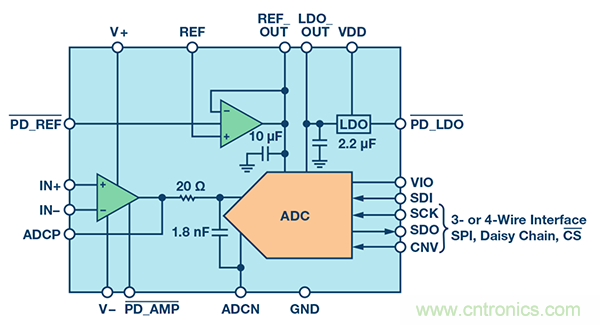

如上所述,要使一個基于SAR ADC的轉(zhuǎn)換系統(tǒng)實現(xiàn)數(shù)據(jù)手冊中的性能,必須考慮到某些設計因素。SAR ADC基準電壓源和模擬輸入源的特性是決定轉(zhuǎn)換信號鏈設計是否成功的關(guān)鍵。通常,一個SARADC需使用一個低阻抗基準電壓源和一個較大的、布置適當?shù)娜ヱ铍娙荨T撆月冯娙萦脕硌a充ADC在SAR位校驗期間消耗的電荷,可看作為ADC外部SAR陣列中的一個元件。ADC還需要一個合適的模擬輸入源,其噪聲性能和帶寬應足以使ADC輸入建立至所需分辨率。圖1顯示了ADAQ798x系列器件的框圖。

圖1. ADAQ798x框圖。

如圖1所示,ADAQ798x內(nèi)置有一個基準電壓緩沖器和一個對應的10 F去耦電容。理論上,該去耦電容應鄰近ADC的參考輸入。如此布置是為了減小去耦電容和SAR電容陣列之間的總體寄生阻抗。該路徑應使阻抗盡可能低,以便電容將電荷快速添加到SAR陣列上,然后在轉(zhuǎn)換過程中重新分布。同時,基準電壓緩沖器和去耦電容之間的走線電阻已受到控制。走線尺寸經(jīng)過精心選擇,確保其所得電阻能使基準電壓緩沖器保持穩(wěn)定,而其造成的電壓降不足以產(chǎn)生轉(zhuǎn)換增益誤差。用于緩沖參考信號的放大器被配置成一個單位增益緩沖器。這樣會形成外部基準電壓源的一個高阻抗輸入,而非SAR ADC參考輸入的傳統(tǒng)型開關(guān)電容負載?,F(xiàn)在,ADAQ798x用戶可以使用一個低功耗或無緩沖基準電壓源來驅(qū)動ADAQ798x的參考輸入 (REFIN) 引腳。由于形成高阻抗,因此也為用戶在選擇基準電壓源的物理PCB位置時提供了更多的靈活性。通過使用此SiP元件,基準電壓源的布局就變得不那么重要,因為ADAQ798x內(nèi)包含一個受到良好控制的基準電壓緩沖器。由于僅包含一個緩沖器,而非基準電壓源本身,用戶可在廣泛范圍內(nèi)自由選擇基準值,從而通過此基準電壓的選擇使系統(tǒng)的動態(tài)范圍最大化。因為基準電壓決定了轉(zhuǎn)換器的滿量程電壓。

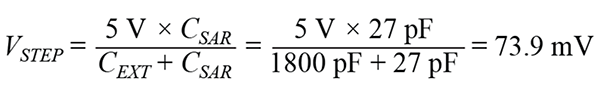

ADAQ798x還具有一個ADC驅(qū)動器以及對應的低通濾波器,濾波器位于驅(qū)動器和ADC輸入之間。濾波器帶寬的選擇是決定器件能否達到所需性能水平的關(guān)鍵因素。帶寬選擇是在高速ADC驅(qū)動器的建立時間和濾波寬帶噪聲之間作一個權(quán)衡。ADC輸入節(jié)點處的任何干擾必須在ADC采集時間內(nèi)建立至足夠的分辨率。當SAR ADC執(zhí)行其轉(zhuǎn)換過程時,ADC輸入與其外部輸入源斷開連接。在轉(zhuǎn)換過程中,ADC輸入的電位可能會發(fā)生變化。盡管如此,轉(zhuǎn)換結(jié)束時SAR電容器陣列上的電壓與轉(zhuǎn)換開始時的電壓基本相同。當ADC返回采集(跟蹤)模式時,SAR電容陣列的負載呈現(xiàn)在ADC輸入端。該電容與外部低通濾波器的電容并聯(lián)。由于這些電容具有不同的電壓,因此會發(fā)生電荷再分布以使所有電容上的電壓達到平衡。這將導致需在采集周期內(nèi)建立的ADC輸入出現(xiàn)電壓階躍。最差情況是在ADC進行滿量程轉(zhuǎn)換時發(fā)生階躍。這種情況可能會出現(xiàn)在采用多路復用輸入的系統(tǒng)中。此電壓階躍會因外部電容和內(nèi)部SAR電容的比率而衰減。ADAQ798x產(chǎn)品均具有一個1800 pF的低通濾波電容。假設基準電壓為5 V,則ADC輸入的最大電壓階躍計算如下:

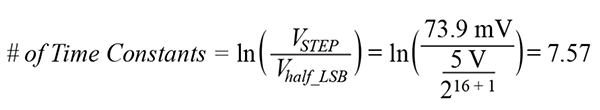

此電壓階躍必須在最小采集時間290 ns內(nèi)建立。建立此電壓階躍所需的時間常數(shù)數(shù)目可通過計算階躍大小和建立誤差之比的自然對數(shù)來獲得。本例中建立誤差為½ LSB。那么,時間常數(shù)的數(shù)目如下:

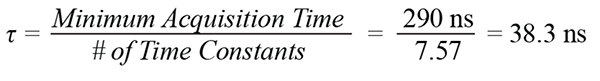

已知時間常數(shù)的數(shù)目后,可以確定出RC低通濾波器的時間常數(shù) (T):

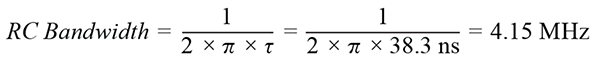

將時間常數(shù)帶入下式可求出所需的濾波器帶寬:

為了提供一定的裕量并使用標準值元件,ADAQ798x產(chǎn)品均具有一個由20 電阻和1800 pF電容構(gòu)成的濾波器。可提供的濾波器帶寬為4.42 MHz,因此ADAQ798x濾波器能夠在ADC采集時間內(nèi)建立最大可期電壓階躍。計算所得的濾波器帶寬也代表了噪聲濾波和建立過程之間的權(quán)衡點。在確保建立過程的前提下選用最低要求附近的濾波器帶寬,將能最大化提高無源低通濾波器的噪聲濾波作用。

雖然SAR ADC返回采集模式時的電壓階躍是濾波器建立計算中的限制因素,值得注意的是,該濾波器也可以在1 s的最小轉(zhuǎn)換周期內(nèi)順利建立多路復用器滿量程階躍帶來的實際電壓變化。將滿量程階躍建立至1/2 LSB分辨率需要11.78個時間常數(shù)。這是根據(jù)N+1個量化級的自然對數(shù)計算而得。在本例中為217或131072個數(shù)字碼。11.78個時間常數(shù),每個時間常數(shù)38.3 ns,那么總共約為450 ns,這個時間相較于1 s轉(zhuǎn)換周期不足為慮。其假設前提是多路復用器通道在轉(zhuǎn)換開始后直接切換。

為確保轉(zhuǎn)換信號鏈的正常性能,ADC驅(qū)動器的帶寬也非常重要。在單位增益配置中,建立過程的限制因素是需在290 ns內(nèi)建立的電壓階躍,其與返回到采集模式的轉(zhuǎn)換器相關(guān)。因此,在這種情況下,小信號帶寬是最重要的放大器帶寬特性。要在1 s的最小轉(zhuǎn)換周期內(nèi)建立多路復用器的滿量程階躍,ADC驅(qū)動器的大信號帶寬必須確保1 s時間周期內(nèi)可處理11.78個時間常數(shù)。

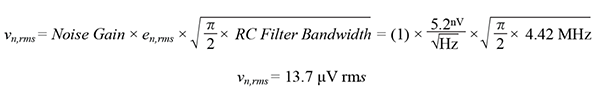

ADC驅(qū)動器不可向轉(zhuǎn)換信號鏈引入過量噪聲。子系統(tǒng)的總體噪聲性能計算為ADC噪聲、ADC驅(qū)動器噪聲和基準電壓緩沖器噪聲的平方和根值 (RSS)。由于旁路電容較大,參考電路的帶寬有限,因此基準電壓緩沖器噪聲在RSS計算中可以忽略不計。在單位增益配置中為ADC驅(qū)動器所選的噪聲目標為不大于ADC噪聲的1/3。ADC驅(qū)動器的額定噪聲頻譜密度為5.2 nV/Hz。要計算整體系統(tǒng)的噪聲,必須使用下式將ADC驅(qū)動器的噪聲頻譜密度轉(zhuǎn)換為V rms:

ADC的典型動態(tài)范圍特性為92 dB,基準電壓為5V。ADC的噪底可以通過下式計算:

ADC驅(qū)動器的噪底為13.7 V rms,在不大于ADC噪聲的1/3目標范圍內(nèi)。單位增益配置中ADC驅(qū)動器引入的噪聲導致整體系統(tǒng)動態(tài)范圍從92 db降至91.6 dB。由于ADC驅(qū)動器對系統(tǒng)噪聲的影響不大,所以,對于因采樣周期較長而提供較長建立時間的低采樣速率應用,無需改變低通濾波器的帶寬。通過降低濾波器帶寬在單位增益上帶來的最佳改善可能是重新獲得動態(tài)范圍損耗的0.4 dB。然而,為降低帶寬而增大濾波器電阻會對THD性能產(chǎn)生不利影響,而ADC驅(qū)動器可能難以驅(qū)動較大的容性負載。如果還需要其他濾波,ADC驅(qū)動器可配置為提供濾波作用。

ADAQ798x產(chǎn)品中還包含一個2.5 V低噪聲CMOS LDO線性穩(wěn)壓器。某些SAR ADC產(chǎn)品需要特定的2.5 V電源,并且要求公差范圍很小。如果用戶沒有可用的2.5 V電源軌,則可能需要專為ADC設計一個電源。而使用此元件則可以大大簡化電源,因為其中包含了LDO。片上LDO用于向轉(zhuǎn)換器供電,此時LDO輸入相當于ADC的電源。這樣可提供更廣泛的可用電源電壓,并且使電路更簡單。放大器的正電源可以作為LDO輸入以實現(xiàn)一個單電源系統(tǒng)。此外,還可選擇適當?shù)碾娫措妷阂詢?yōu)化性能或功耗。該器件支持全掉電模式。電源配置的靈活性使ADAQ798x用戶可針對具體應用作出最合適的權(quán)衡。

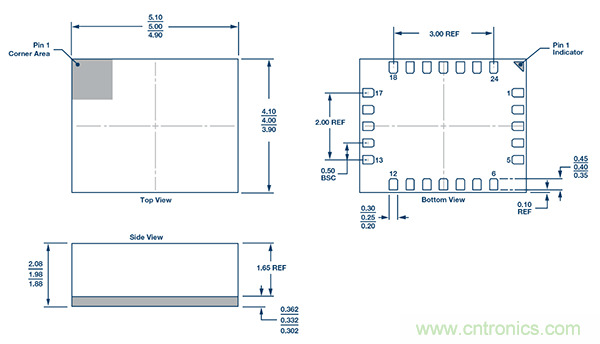

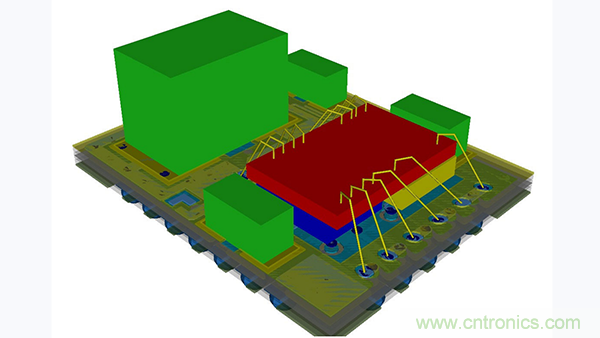

ADAQ798x的封裝尺寸為5 mm × 4 mm × 2 mm。四層層壓片厚0.35 mm,塑封片厚1.65 mm。這種壓模成形封裝的特點如同任何典型封裝集成電路,采用全塑封料和底部填充工藝。用戶所見的層壓片呈LGA封裝,具有24個I/O焊盤。圖2顯示了ADAQ798x的封裝外形圖。圖3為無任何封裝或塑封的ADAQ798x裝配模型。從圖3可以看出,該子系統(tǒng)混合運用了ADI有源器件和公開市場上常見的無源器件。層壓片走線的設計有利于控制阻抗并消除任何串擾。正是因為在所有這些設計和裝配技術(shù)上取得的成果,我們開發(fā)出的產(chǎn)品可以比同類器件設計節(jié)省高達50%的PCB面積。

圖2. ADAQ798x的封裝外形圖。

圖3. ADAQ798x的三維裝配模型。

除了節(jié)省面積之外,ADAQ798x還為信號鏈設計工程師實現(xiàn)所需性能和降低系統(tǒng)設計風險提供了更佳的機會。從根本上說,這樣可以縮短上市時間和降低開發(fā)成本。選用ADAQ798x還可以簡化系統(tǒng)的物料清單,一份數(shù)據(jù)手冊可涵蓋系統(tǒng)中的更多部分。此款SiP器件堅固耐用。專為承受惡劣的工業(yè)環(huán)境而設計,并已通過大量測試驗證其合格性。它能夠?qū)崿F(xiàn)絕佳的質(zhì)量等級,額定溫度范圍為–55°C至+125°C。總而言之,ADAQ798x實現(xiàn)了集成度與靈活性之間的卓越平衡,并且不會犧牲信號鏈的性能。

作者:Ryan Curran

Ryan Curran 是ADI 公司精密轉(zhuǎn)換器業(yè)務部門的一名產(chǎn)品應用工程師。自2005 年加盟ADI 以來,他一直主要從事SAR ADC 方面工作。Ryan 獲緬因大學歐洛諾電子工程學士學位,目前在阿默斯特馬薩諸塞大學伊森伯格管理學院攻讀工商管理碩士學位。

本文轉(zhuǎn)載自ADI電機控制中文技術(shù)社區(qū)。

推薦閱讀: