【導(dǎo)讀】針對高分辨率、精密ADC應(yīng)用中的雜散問題,本文將介紹幾種判斷其根本原因的方法,并提出相應(yīng)的解決方案。這些技術(shù)和方法將有助于提高終端系統(tǒng)的EMC能力和可靠性。

簡介

雖然目前的高分辨率SAR ADC和Σ-Δ ADC可提供高分辨率和低噪聲,但系統(tǒng)設(shè)計師們可能難以實現(xiàn)數(shù)據(jù)手冊上的額定SNR性能。而要達(dá)到最佳SFDR,也就是在系統(tǒng)信號鏈中實現(xiàn)無雜散的干凈噪底,可能就更加困難了。雜散信號可能源于ADC周圍的不合理電路,也有可能是因惡劣工作環(huán)境下出現(xiàn)的外部干擾而導(dǎo)致。

針對高分辨率、精密ADC應(yīng)用中的雜散問題,本文將介紹幾種判斷其根本原因的方法,并提出相應(yīng)的解決方案。這些技術(shù)和方法將有助于提高終端系統(tǒng)的EMC能力和可靠性。

本文將針對五種不同的應(yīng)用情況闡述用于降低雜散的特定設(shè)計解決方案:

1.由控制器板上的DC-DC電源輻射而導(dǎo)致的雜散問題。

2.由AC-DC適配器噪聲通過外部基準(zhǔn)源而導(dǎo)致的雜散問題。

3.由模擬輸入電纜而導(dǎo)致的雜散問題。

4.由模擬輸入電纜上的耦合干擾而導(dǎo)致的雜散問題。

5.由室內(nèi)照明設(shè)備導(dǎo)致的雜散問題。

雜散與SFDR

眾所周知,無雜散動態(tài)范圍(SFDR)表示可從大干擾信號分辨出的最小功率信號。對于目前的高分辨率、精密ADC,SFDR一般主要由基波頻率與目標(biāo)基波頻率的第二或第三諧波之間的動態(tài)范圍構(gòu)成。然而,由于系統(tǒng)其他方面的因素,可能會導(dǎo)致雜散產(chǎn)生并限制系統(tǒng)的性能。

這些雜散可分為輸入頻率相關(guān)雜散和固定頻率雜散。輸入頻率相關(guān)雜散與諧波或非線性特性有關(guān)。本文將重點分析由電源、外部基準(zhǔn)源、數(shù)字連接、外部干擾等造成的固定頻率雜散。根據(jù)應(yīng)用情況,可降低或完全避免這些類型的雜散,以助于實現(xiàn)最佳的信號鏈性能。 由ADC周圍DC-DC電源而導(dǎo)致的雜散問題

由于DC-DC開關(guān)穩(wěn)壓器會產(chǎn)生較高的紋波噪聲,通常建議將LDO作為在精密測量系統(tǒng)中為精密ADC生成低噪聲電源軌的解決方案。固定頻率或脈寬調(diào)制開關(guān)穩(wěn)壓器會產(chǎn)生開關(guān)紋波,該紋波一般位于幾萬至幾兆赫茲固定頻率處。固定頻率噪聲可能會通過ADC的PSRR機(jī)制饋入ADC轉(zhuǎn)換代碼中。

某些設(shè)計師可能會因電路板空間有限或預(yù)算問題而在精密ADC應(yīng)用中采用DC-DC開關(guān)穩(wěn)壓器。為了實現(xiàn)理想的信號鏈性能,他們必須限制紋波噪聲或使用高PSRR ADC,以確保這些紋波噪聲低于ADC噪底。否則,在ADC輸出頻譜的開關(guān)頻率處可能會出現(xiàn)雜散,這有可能會使信號鏈的動態(tài)范圍降級。

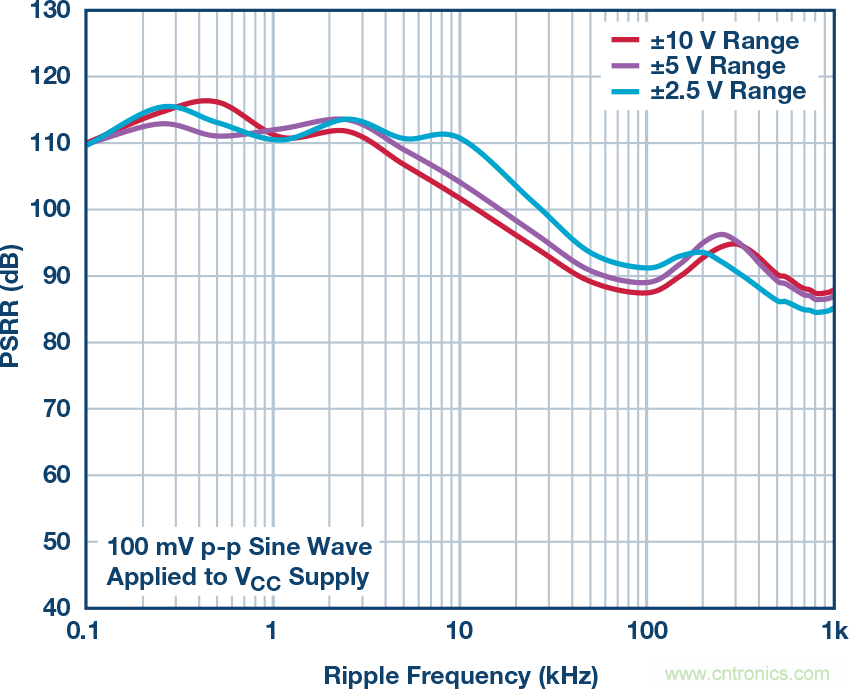

AD7616 是一款16位數(shù)據(jù)采集系統(tǒng)(DAS),支持在電力線監(jiān)控中對16個通道進(jìn)行雙路同步采樣。該器件具有很高的PSRR,將能有效地抑制/衰減開關(guān)紋波。例如,將一個在100 kHz處有100 mV峰峰值紋波噪聲的DC-DC開關(guān)電源用于AD7616,VCC為5 V,±10 V輸入范圍。

則因紋波導(dǎo)致的數(shù)字碼噪聲為:

對于一個16位轉(zhuǎn)換器而言,ADC輸出端出現(xiàn)的這種紋波電平是非常低的。ADC的高PSRR性能使得設(shè)計師們也可以在精密測量系統(tǒng)中采用開關(guān)穩(wěn)壓器。

圖1.AD7616 PSRR與紋波頻率的關(guān)系。

因DC-DC電源輻射而導(dǎo)致的雜散問題

僅僅使用高PSRR ADC并不能保證開關(guān)穩(wěn)壓器在精密測量系統(tǒng)中不會造成任何問題。開關(guān)穩(wěn)壓器產(chǎn)生的紋波噪聲可能會通過其他方式饋入ADC的數(shù)字碼中。

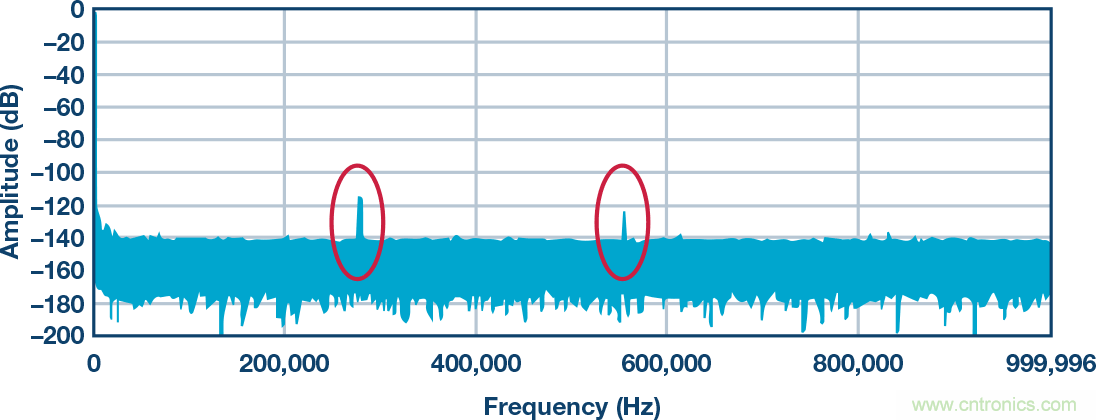

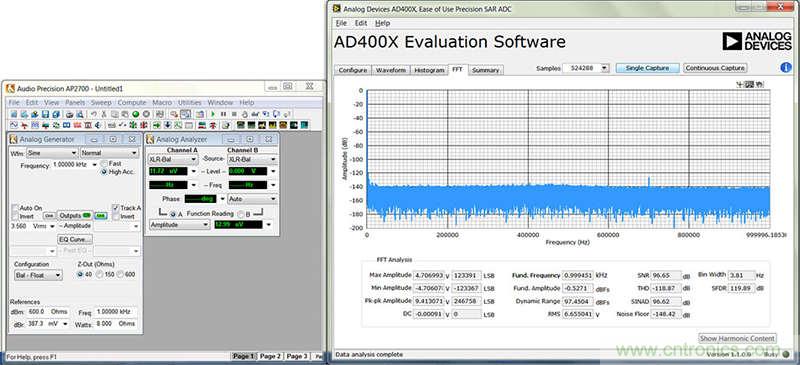

AD4003 是一款低噪聲、低功耗、高速、18位、2 MSPS精密逐次逼近型寄存器(SAR) ADC。在EVAL-AD4003FMCZ評估板交流性能測試過程中,在277.5 kHz附近出現(xiàn)約–115 dBFS的雜散電平;該雜散及其第二諧波如圖2所示。

圖2.EVAL-AD4003FMCZ評估板上觀察到的雜散問題。

其次,進(jìn)行測試,判斷雜散是否來自模擬輸入端。測試結(jié)果如下:

移除差分模擬輸入調(diào)理電路后,雜散降低。

在AD4003的緩沖放大器ADA4807-1前端插入一個窄帶RC濾波器(如1 kΩ,10 nF)后,雜散降低。

這些結(jié)果表明,雜散導(dǎo)致的噪聲可能會通過調(diào)理電路進(jìn)入AD4003的模擬輸入端。然后,斷開傳感器輸出,移除調(diào)理電路,僅留下VREF/2 CM電壓輸入(在ADA4807-1的同相輸入端)。但仍然存在雜散,并且具有近似的電平。

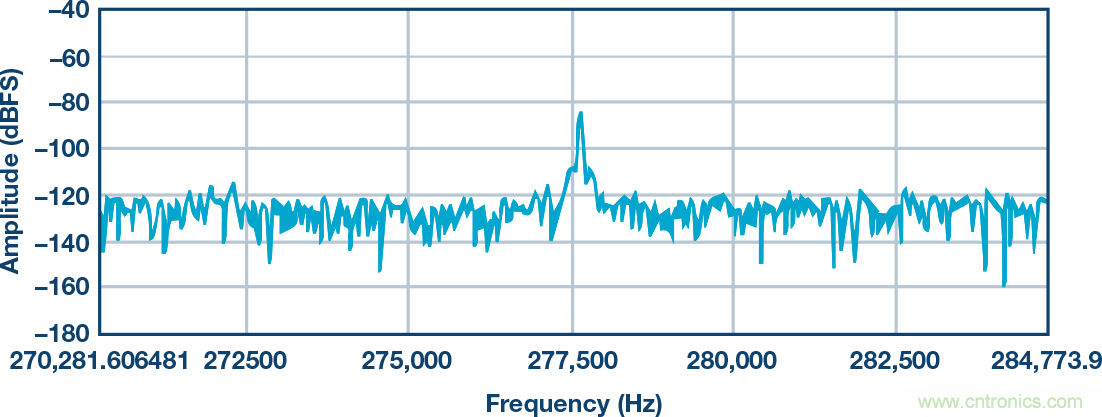

那么,懷疑干擾源有可能位于EVAL-AD4003FMCZ信號鏈周圍。為了證明此點,在EVAL-AD4003FMCZ評估板和SDP-H1控制器板上多處放置銅箔屏蔽罩。其結(jié)果是,當(dāng)銅箔屏蔽罩覆蓋SDP-H1板上的DC-DC電源時,如圖3所示,雜散就會消失。277.5 kHz雜散頻率剛好與ADP2323 穩(wěn)壓器的編程開關(guān)頻率相符。圖4顯示了EVAL-AD7616SDZ GUI FFT捕獲的3.3 V VADJ_FMC開關(guān)頻率功率。

圖3.VADJFMC電感L5被銅箔屏蔽罩覆蓋。

圖4.EVAL-AD7616SDZ GUI FFT捕獲的VADJFMC 3.3 V開關(guān)紋波。

得出的結(jié)論是,DC-DC開關(guān)頻率干擾是由8.2 µH電感L5發(fā)出的。該干擾從緩沖放大器ADA4807-1的輸入端注入信號鏈,然后進(jìn)入AD4003 ADC的模擬輸入端。

針對這種DC-DC電源轉(zhuǎn)換器導(dǎo)致的雜散問題,可行的解決方案有:

1.在AD4003 ADC前端使用一個低通濾波器,以在應(yīng)用帶寬允許的情況下,將耦合的DC-DC開關(guān)頻率干擾衰減到符合設(shè)計目標(biāo)的程度(即雜散位于噪底以下)。

2.使用L5為屏蔽電感的新型SDP-H1板(BOM版本1.4)。輻射干擾功率降低,因此AD4003 ADC頻譜中捕獲的雜散功率也低得多。

3.VADJ_FMC的電壓電平可通過EVAL-AD4003FMCZ評估板上的EEPROM進(jìn)行編程。試驗證明,使用較低的電壓電平(如VADJ_FMC為2.5 V)也會使雜散消失。

由AC-DC適配器噪聲耦合通過外部基準(zhǔn)源而導(dǎo)致的雜散問題

ADC參考其直流基準(zhǔn)電壓電平將模擬信號量化成一個數(shù)字碼。因此,直流基準(zhǔn)電壓輸入上的噪聲將直接饋入ADC輸出的數(shù)字碼。

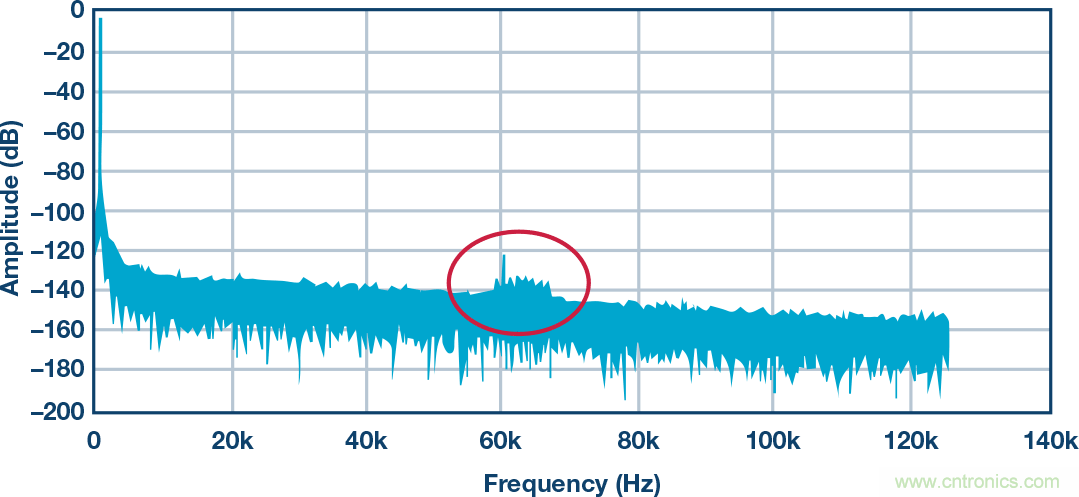

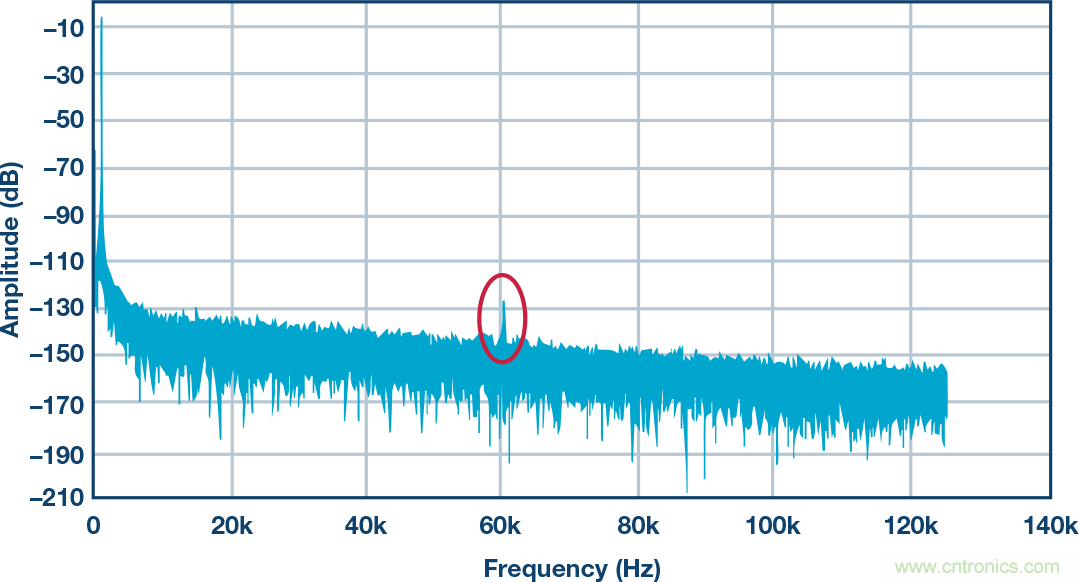

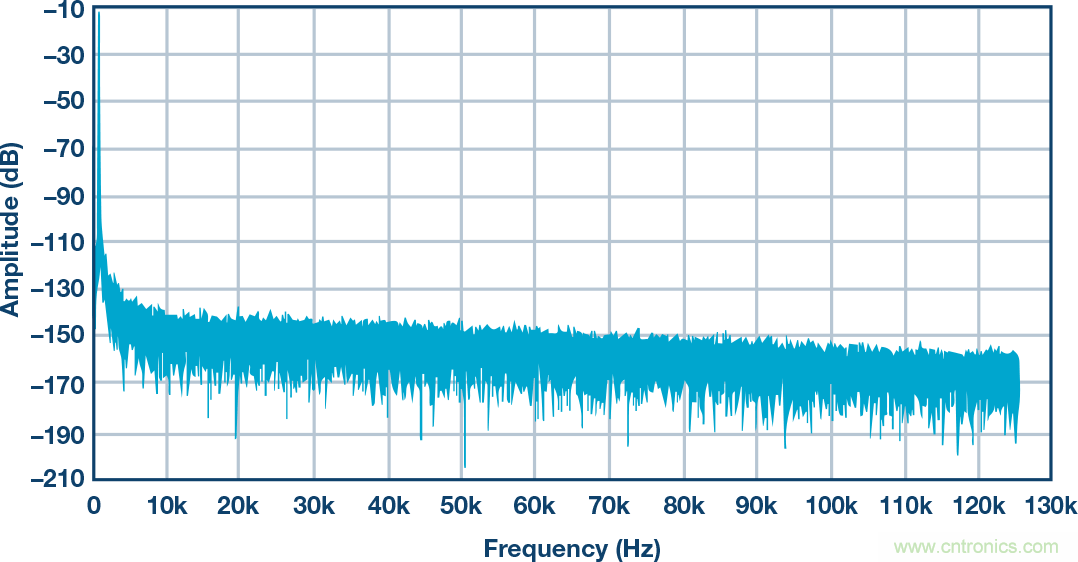

AD7175-2是一款低噪聲、快速建立、多路復(fù)用、2/4通道(全差分/偽差分)Σ-Δ型ADC,可用于低帶寬輸入。在EVAL-AD7175SDZ評估板的信號鏈測試中,在60 kHz附近捕獲到一簇雜散信號,如圖5所示。

圖5.EVAL-AD7175-2SDZ評估板上觀察到的雜散問題。

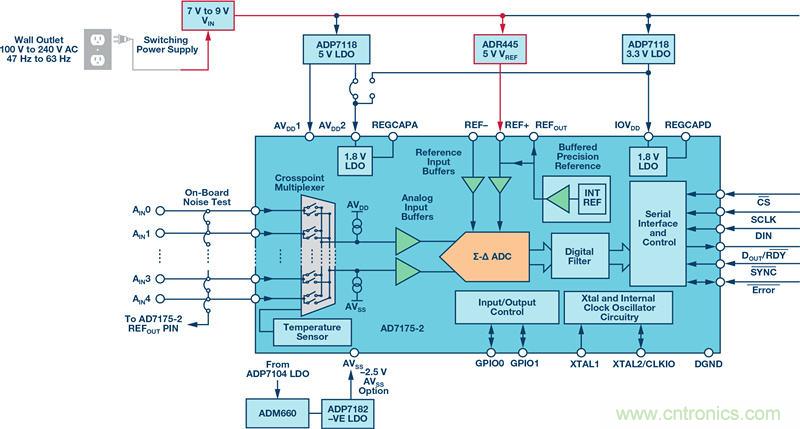

經(jīng)過評估發(fā)現(xiàn),AD7175-2 ADC的電源和模擬調(diào)理電路都處于良好狀態(tài)。但是,如圖6中所示,AD7175-2的5 V基準(zhǔn)電壓輸入由ADR445基準(zhǔn)源生成,該基準(zhǔn)源的9 V直流電源來自評估板外部的AC-DC適配器。接下來,使用一個工作臺9 V直流電源模塊替換該適配器。結(jié)果雜散簇消失,僅在60 kHz處留下一個窄帶雜散。

圖6.EVAL-AD7175-2SDZ評估板上觀察到雜散問題。

圖7.EVAL-AD7175-2SDZ評估板上已消除雜散簇。

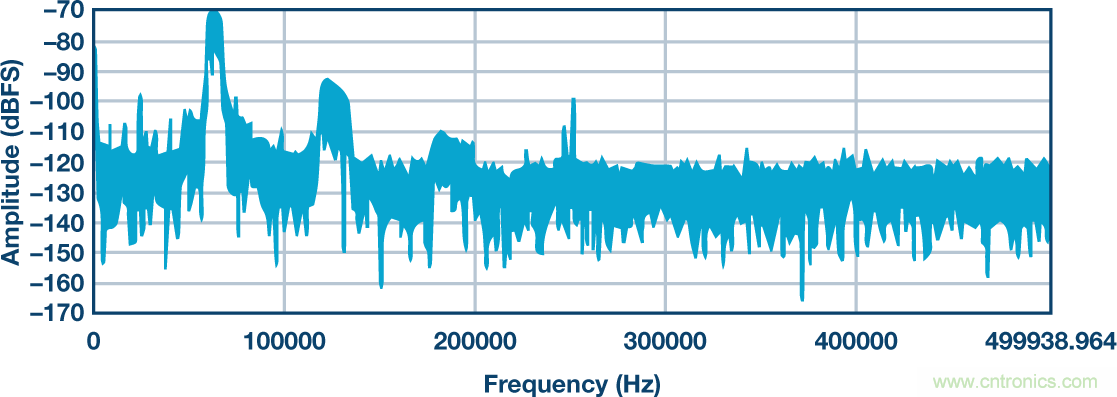

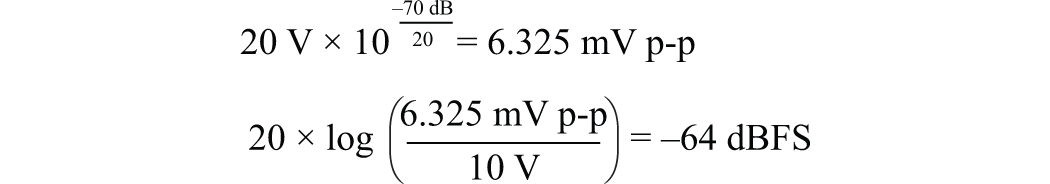

以320 mA輸出電流對EVAL-AD7175-2SDZ板供電時,通過EVAL-AD7616SDZ GUI FFT對9V輸出AC-DC適配器進(jìn)行測試。使用AD7616 ±10 V輸入范圍時,ADR445 基準(zhǔn)源電源引腳上的開關(guān)頻率功率約為 –70 dBFS,這意味著使用AD7175-2 ±5 V輸入范圍時,產(chǎn)生的噪聲具有6.325 mV峰峰值或為–64 dBFS。

圖8.EVAL-AD7616SDZ GUI FFT捕獲的3.3 V VADJFMC開關(guān)紋波。

此電源開關(guān)紋波噪聲會饋入AD7175-2 ADC,并以數(shù)字碼呈現(xiàn),存在一定程度的衰減,如下所述:

ADR445基準(zhǔn)源的數(shù)據(jù)手冊規(guī)定60 kHz處的PSRR為49 dB。

2.ADR445基準(zhǔn)源在60 kHz處的輸出阻抗約為4.2 Ω。結(jié)合4.8 µF存儲電容,可進(jìn)一步造成18 dB衰減。

3.此外,當(dāng)ODR為256 ksps時,AD7175-2 ADC的數(shù)字濾波器sinc5 + sinc1在60 kHz處會增加約–3 dB衰減。

計算所得的電平為–134 dBFS,十分接近圖5中所捕獲的–130 dBFS雜散簇電平(不包括最高的窄帶雜散)。這可證實,該雜散簇是由AC-DC適配器的開關(guān)紋波饋入外部基準(zhǔn)源ADR445造成的。剩下的窄帶雜散將在下一章節(jié)中予以分析。

由注入信號鏈的干擾而導(dǎo)致的雜散問題

在硬件系統(tǒng)中,從輸入傳感器到精密轉(zhuǎn)換器輸入端之間往往具有很長一段信號鏈。該信號鏈包括連接電纜、連接器、路由導(dǎo)線、調(diào)整和調(diào)理電路、ADC驅(qū)動器等等。因此,外部干擾很有可能會注入模擬輸入信號鏈并產(chǎn)生ADC雜散。 由電源電纜干擾注入信號鏈而導(dǎo)致的雜散問題

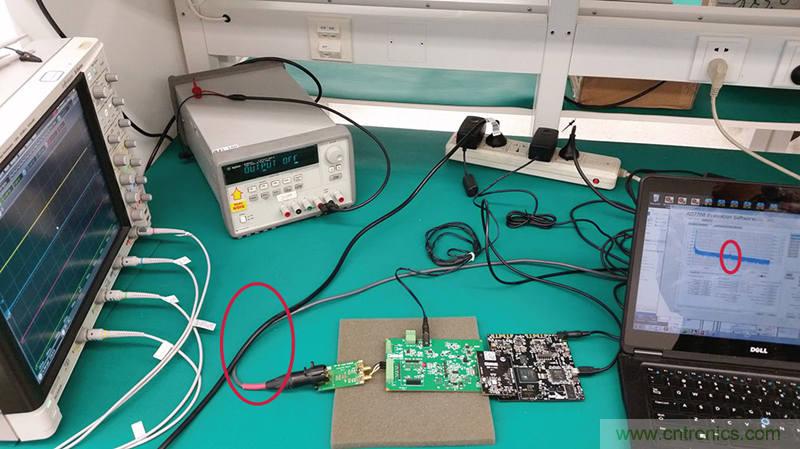

在研究EVAL-AD7175-2SDZ評估板輸出頻譜中剩下的窄帶雜散時,注意到測試臺上有一臺正在工作的數(shù)字示波器。如圖9所示,該示波器的220 V交流電源電纜(黑色)與EVAL-AD7175-2SDZ評估板的模擬輸入電纜(灰色)有一部分重疊。將示波器關(guān)掉或?qū)⑵潆娫措娎|從模擬輸入電纜上移開后,60 kHz處的窄帶雜散消失,如圖10所示。

在系統(tǒng)機(jī)柜中,對傳感器至DAQ板之間的線路進(jìn)行布線時應(yīng)格外注意。將敏感的低電平模擬信號與大電流電力線隔離開來是一個良好的操作習(xí)慣。

圖9.示波器電源電纜導(dǎo)致的雜散

圖10.EVAL-AD7175-2SDZ評估板上已消除所有雜散。

由燈具輻射導(dǎo)致的雜散問題

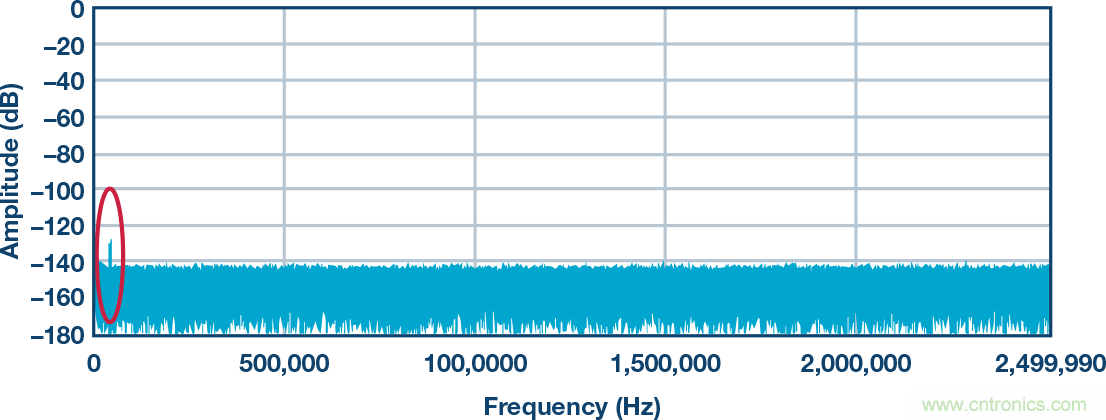

在測試EVAL-AD7960FMCZ評估板時,F(xiàn)FT頻譜上出現(xiàn)一個雜散。如圖11所示,該雜散的電平約–130 dB,位于40 kHz處。

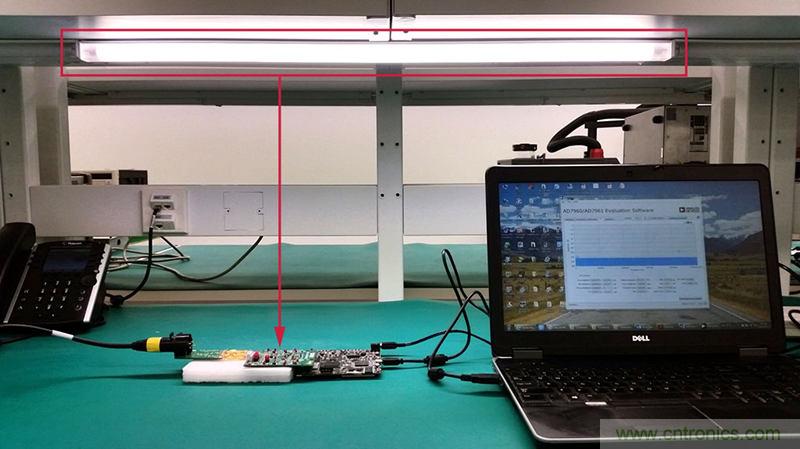

40 kHz似乎與EVAL-AD7960FMCZ評估板及其控制器板SDP-H1上的任何信號頻率都不相關(guān)。找出雜散源的另一種方法是清理測試臺,也許是測試臺上的某些物體產(chǎn)生了外部干擾。當(dāng)關(guān)掉臺架上的日光燈后,雜散消失。此外還發(fā)現(xiàn),EVAL-AD7960FMCZ評估板離日光燈越近,40 kHz處的雜散就會越高。在緩沖放大器ADA4899-1前方插入一個額外的RC濾波器(如1 kΩ,10 nF)后,雜散降低約10 dB。這意味著,日光燈輻射干擾從緩沖放大器的同相輸入端前方進(jìn)入到信號鏈路中。 對于工作在照明環(huán)境下的系統(tǒng),在前端電路上安裝一個屏蔽罩有助于防止輻射干擾和優(yōu)化信號鏈性能。

對于工作在照明環(huán)境下的系統(tǒng),在前端電路上安裝一個屏蔽罩有助于防止輻射干擾和優(yōu)化信號鏈性能。

圖11.日光燈輻射在EVAL-AD7960FMCZ上造成的雜散

圖12.靠近EVAL-AD7960FMCZ評估板的日光燈。

由較長模擬輸入電纜導(dǎo)致的雜散問題

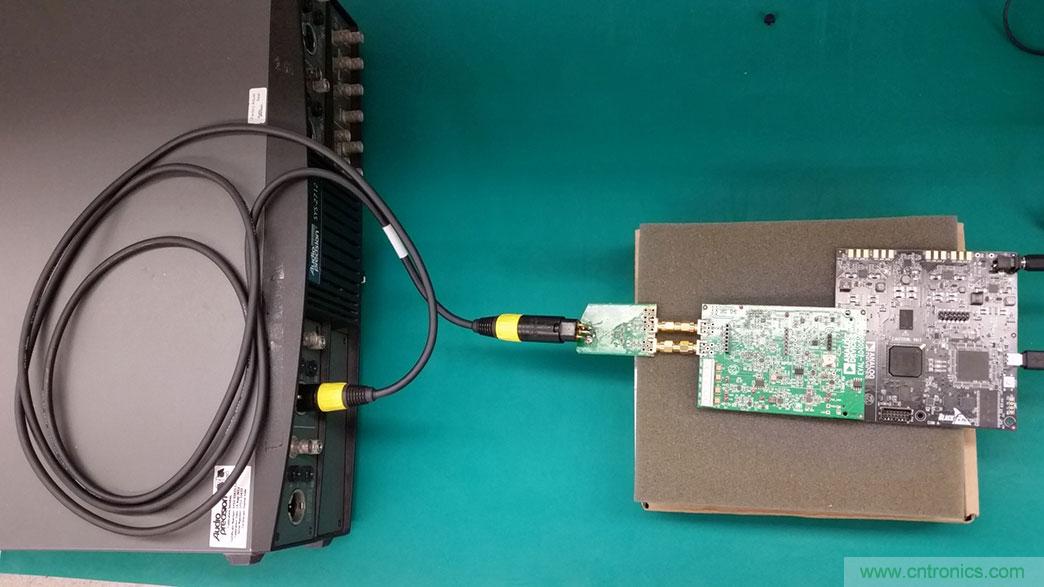

在EVAL-AD4003FMCZ評估板的工作過程中,使用的AP SY2712信號發(fā)生器通過一條XLR麥克風(fēng)電纜(約2米長)驅(qū)動低噪聲、低THD正弦波信號進(jìn)入模擬輸入端。在這種設(shè)置下,700 kHz處出現(xiàn)一個約–125 dB的雜散,如圖13所示。

在研究該雜散的過程中,發(fā)現(xiàn)有三種方法可解決此問題:

不用兩米長的XLR麥克風(fēng)電纜,而直接將AP平衡輸出的XLR插針與轉(zhuǎn)接板的XLR插口短接。

將信號源SY2712的輸出阻抗設(shè)置從Z-Out = 40 Ω改為Z-Out = 600 Ω。

在AD4003的緩沖放大器ADA4807-1前端向信號鏈中插入一個窄帶RC濾波器(如1 kΩ,10 nF)后,雜散降低。

最終結(jié)論是,在700 kHz處出現(xiàn)的高頻雜散是由于信號源輸出阻抗不匹配并且XLR電纜較長所導(dǎo)致。

圖13.XLR電纜在EVAL-AD4003FMCZ上造成的雜散

圖14.AP通過較長的XLR電纜驅(qū)動EVAL-AD4003FMCZ。

結(jié)論

針對系統(tǒng)應(yīng)用中高分辨率、精密ADC的雜散問題,本文探討了判斷其根本原因的方法。文中介紹了在五種不同應(yīng)用情況下消除或降低雜散的特定設(shè)計解決方案。本文還探討了相關(guān)的雜散計算方法,有助于評估雜散的功率水平(作為特定應(yīng)用的設(shè)計目標(biāo))。

推薦閱讀: