【導(dǎo)讀】能量采集允許智能傳感器部署在先前不可能部署的更廣泛情況中�����,是實(shí)現(xiàn)新一代設(shè)備的關(guān)鍵�����。這類傳感器可以進(jìn)行連續(xù)的狀態(tài)監(jiān)測(cè)���,能夠用于林林總總不同的應(yīng)用中�����,比如工業(yè)馬達(dá)�����,以至穿戴在身體上的長(zhǎng)期健康測(cè)量裝置�。

雖然這些系統(tǒng)可以使用電池供電���,所以不需要將傳感器與主電源連接�����,但是仍然需要更換電池或充電�����。一旦放置在大型馬達(dá)或渦輪機(jī)附近�,便很難觸及和更換電池����。不過,許多這些應(yīng)用的優(yōu)點(diǎn)是它們可以自己提供能量���,自給自足���。

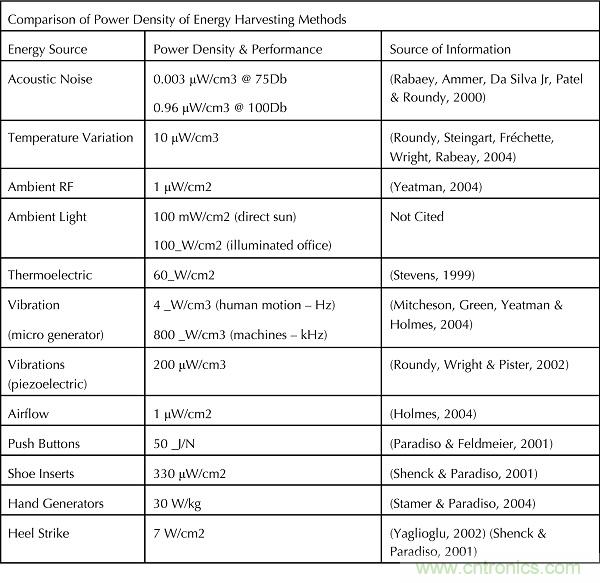

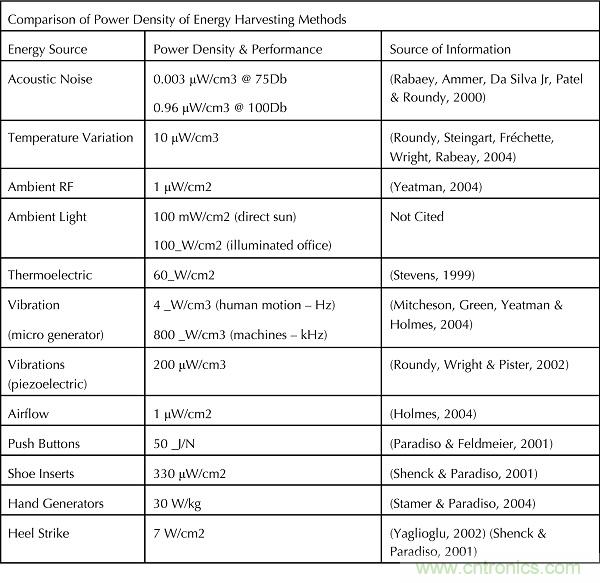

只要通過合適的地震量(慣性質(zhì)量)和轉(zhuǎn)換器����,便可利用工業(yè)馬達(dá)的振動(dòng)為監(jiān)測(cè)它的系統(tǒng)提供能量。穿戴在身體上的傳感器的情況類似�����,采集到的振動(dòng)和熱能可以使得電荷呈涓流形式進(jìn)入電容器內(nèi)�����,用于傳感器供電(圖1)���。

圖1:各種能量采集方法的功率密度(來源:技術(shù)研究雜志)

雖然這些系統(tǒng)提供了采集能量的機(jī)制����,但是它們很少能夠達(dá)到設(shè)計(jì)人員習(xí)慣使用的電池供電系統(tǒng)的功率水平。因此�����,設(shè)計(jì)一種功率消耗盡可能低的系統(tǒng)是至關(guān)重要的���。

降低邏輯電路功率的關(guān)鍵目標(biāo)是供電電壓���。在CMOS電路中,電壓和功耗之間呈平方關(guān)系���,如公式P = CV2f所示�����,其中C是電路電容���,f是開關(guān)頻率,V是施加的電壓�。從中可以明顯看出,降低電壓可以最大可能地降低功耗���。晶體管近閾值和亞閾值運(yùn)作提供了一種獨(dú)特方法���,可以將微控制器和其它邏輯電路的供電電壓降低到遠(yuǎn)低于標(biāo)準(zhǔn)邏輯電路要求的水平�����。

近閾值和亞閾值運(yùn)作的背后原理,就是器件通常被認(rèn)為“開啟”的閾值電壓其實(shí)并不需要視為邏輯和模擬電路的目標(biāo)�。為了給伴隨每個(gè)柵極的電容路徑充電,邏輯晶體管傳統(tǒng)上被設(shè)計(jì)為飽和時(shí)通過高電流水平����;但是,給這些電路路徑充電時(shí)����,可以不將晶體管開關(guān)到完全飽和狀態(tài),而是允許電流更為緩慢地涓涓流過�。這樣的結(jié)果是開關(guān)邏輯狀態(tài)會(huì)變得緩慢,但是�����,在典型傳感器應(yīng)用中���,其實(shí)不需要以最高可能速度進(jìn)行開關(guān)���。

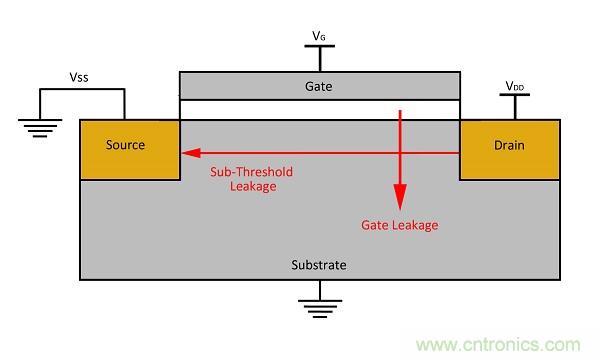

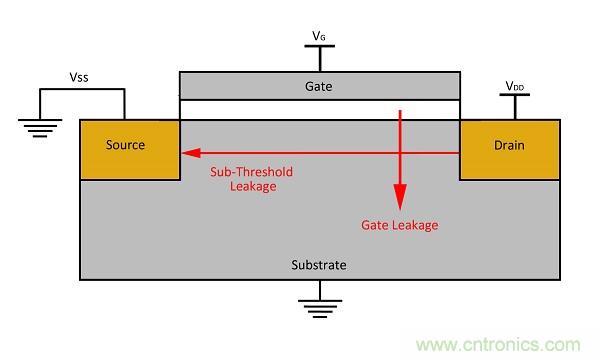

然而����,由于閾值電壓在更低水平驅(qū)動(dòng)�,所以晶體管泄漏電流呈指數(shù)級(jí)增加(圖2)。

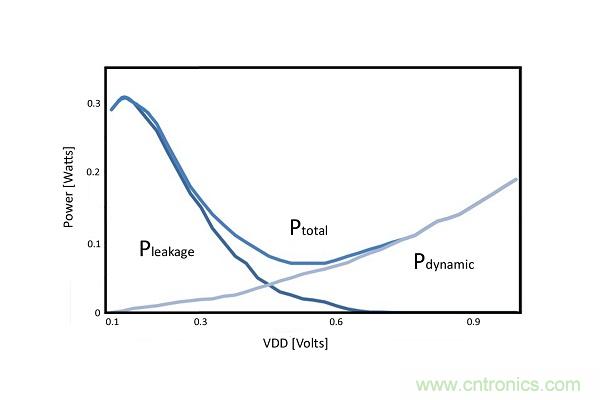

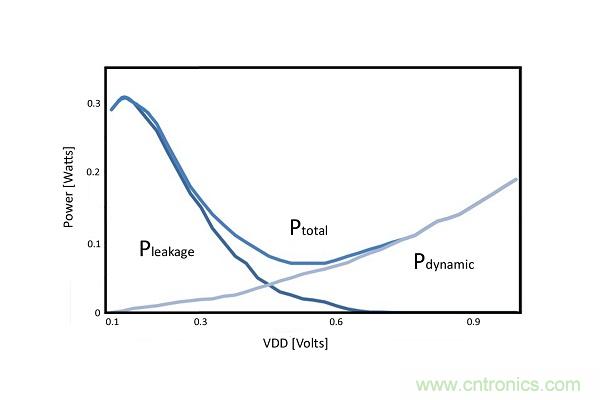

當(dāng)電壓進(jìn)一步下降到深度亞閾值范圍時(shí)���,泄漏損失的能量比例將占優(yōu)勢(shì)�,除了性能考慮�,還引致考慮供電電壓能夠降低到什么程度的次級(jí)限制(圖3)。

對(duì)亞閾值電路設(shè)計(jì)人員來說�,關(guān)鍵問題是在供電電壓接近閾值時(shí)的過程變化和其影響。有效設(shè)計(jì)亞閾值電路的關(guān)鍵���,就是降低這種變化的影響的機(jī)制�,例如專為克服這種變化而設(shè)計(jì)的適應(yīng)性電路����。美國(guó)密歇根大學(xué)和Ambiq Micro進(jìn)行了多年研究,帶來了這種技術(shù)等多項(xiàng)亞閾值技術(shù)創(chuàng)新�。為了有效地利用這項(xiàng)技術(shù),還必須對(duì)整個(gè)設(shè)計(jì)流程進(jìn)行重新設(shè)計(jì)�,包括從實(shí)施亞閾值邏輯電路的標(biāo)準(zhǔn)元件庫(kù)直到測(cè)定納安和皮安電流的測(cè)試策略�。只有通過這種投資水平����,才可能最大限度地提高亞閾值設(shè)計(jì)的節(jié)能效益。

雖然亞閾值運(yùn)作最大程度地利用了電壓和功耗之間的平方關(guān)系���,但是�����,它并非在所有情況下也是最適合的晶體管運(yùn)作方案選擇。由于亞閾值運(yùn)作的性能影響�����,它對(duì)近閾值甚至傳統(tǒng)超閾值方案等使用較高電壓的電路有益處�����。例如�,存儲(chǔ)塊在存取時(shí)不一定能夠從超低電壓運(yùn)作中受益。

在設(shè)計(jì)節(jié)能微控制器時(shí)�����,重要的是在電路水平方面分析電壓、功率和性能之間的折衷權(quán)衡���。這項(xiàng)工作已經(jīng)在Apollo系列微控制器的核心Ambiq亞閾值功率優(yōu)化技術(shù)(SPOT)平臺(tái)上進(jìn)行了廣泛的實(shí)施��。

雖然電路水平設(shè)計(jì)選擇將在優(yōu)化能量采集功率物聯(lián)網(wǎng)(IoT)應(yīng)用中發(fā)揮作用����,但是�����,系統(tǒng)級(jí)的決策對(duì)于總能耗也有著十分重大的影響���。關(guān)鍵舉措是盡可能減少不必要的活動(dòng)�����,這通常使用智能應(yīng)用的睡眠模式來實(shí)現(xiàn)����。采用最大限度地提高每個(gè)時(shí)鐘周期所執(zhí)行工作量的處理器架構(gòu)��,還可以實(shí)現(xiàn)進(jìn)一步的提升��。

微控制器通常具有不止一個(gè)低功耗睡眠模式�����,從局部存儲(chǔ)器和大多數(shù)外設(shè)保持供電但CPU內(nèi)核本身待機(jī)的輕度睡眠模式�����,直到大多數(shù)功能禁用和掉電的深度睡眠模式����。由于越來越少的外設(shè)和內(nèi)核功能保持啟用,因此增加了節(jié)省的能量��。但是����,這種設(shè)計(jì)存在重大的折衷�����。

一般說來��,IoT傳感器節(jié)點(diǎn)需要對(duì)其周圍的環(huán)境進(jìn)行監(jiān)測(cè)����,并在系統(tǒng)條件發(fā)生變化時(shí)做出反應(yīng)��。對(duì)于低功耗嵌入式系統(tǒng)���,特別是在采用能量采集系統(tǒng)時(shí)依賴間歇電源的嵌入式系統(tǒng)來說,優(yōu)化的關(guān)鍵就是找到仍然能夠?qū)?shí)時(shí)事件做出適當(dāng)反應(yīng)的最低功耗睡眠模式�����。

在實(shí)際系統(tǒng)中的微控制器最低能量睡眠模式����,一般是由實(shí)時(shí)時(shí)鐘處理基本的內(nèi)務(wù)管理功能,并且定期喚醒系統(tǒng)來檢查活動(dòng)����。例如每秒喚醒系統(tǒng)以檢查外部條件的變化,如果需要軟件處理輸入的話���,便轉(zhuǎn)而完全喚醒處理器內(nèi)核�����。但是���,在報(bào)警情況相當(dāng)少���,而且間隔并不均勻的系統(tǒng)中,這種輪詢式方法是非常浪費(fèi)的����。

如果讓系統(tǒng)使用較高能量的睡眠狀態(tài)來處理I/O,一旦超過閾值便可以快速喚醒處理器內(nèi)核�����,從而確保對(duì)隨機(jī)中斷做出更快的響應(yīng)���;但是這些模式可能消耗能量庫(kù)��,使得處理器沒有足夠的功率來響應(yīng)。但是���,我們有可能可以結(jié)合深度睡眠模式的長(zhǎng)處��,而仍然對(duì)關(guān)鍵輸入作出快速響應(yīng)�����。

有些超低能量實(shí)時(shí)時(shí)鐘設(shè)計(jì)可以檢測(cè)外部事件����,例如硬件中斷引起的問題或比較器感測(cè)到的輸入電壓變化。當(dāng)檢測(cè)到外部事件時(shí)�����,系統(tǒng)可迅速轉(zhuǎn)向喚醒狀態(tài)�����,不會(huì)因?yàn)閳?zhí)行輪詢策略而引起功率損失��,并且最大限度地延長(zhǎng)了系統(tǒng)處于深度睡眠模式的時(shí)間�����。

在處理軟件時(shí)����,重要的是確保每個(gè)時(shí)鐘周期可以實(shí)現(xiàn)最高工作量。在傳遞給用戶與/或云端之前�����,許多IoT傳感器應(yīng)用需要使用信號(hào)處理算法來檢測(cè)問題和預(yù)處理數(shù)據(jù)。這不僅要求使用32位處理器架構(gòu)而不是8位處理器架構(gòu)(因?yàn)?2位處理器只需更少的周期便可處理這些數(shù)學(xué)運(yùn)算)��,而且要求采用全面支持定點(diǎn)和浮點(diǎn)信號(hào)處理指令的架構(gòu)��。用于浮點(diǎn)運(yùn)算的硬件支持�����,可以確保在減少很多的周期內(nèi)完成運(yùn)算���,從而允許內(nèi)核快速返回到更節(jié)能的睡眠狀態(tài)����,進(jìn)一步降低總體系統(tǒng)級(jí)能耗���。這種要求組合需要選擇ARM Cortex-M4F這樣的處理器����,也就是Ambiq Apollo系列所采用的處理器��。

由于能效提升從系統(tǒng)級(jí)降低到低電壓水平的電路運(yùn)作�����,將電壓控制推動(dòng)到極限����,使得能量采集能夠成為物聯(lián)網(wǎng)日益廣泛的傳感器設(shè)計(jì)的可行選擇。