【導(dǎo)讀】本系列第一部分介紹了鎖相環(huán)(PLL)���,說明了其基本架構(gòu)和工作原理。 另外舉例說明了PLL在通信系統(tǒng)中的用途����。 在第二部分中,我們?cè)敿?xì)考察了相位噪聲�����、參考雜散、輸出漏電流等關(guān)鍵性能規(guī)格����,還考慮了它們對(duì)系統(tǒng)性能的影響���。 在本部分中����,我們將考察PLL頻率合成器的主要構(gòu)建模塊�����。 我們還將比較整數(shù)N和小數(shù)N架構(gòu)�����。 最后將總結(jié)市場(chǎng)上現(xiàn)有的VCO����,同時(shí)列出ADI的現(xiàn)有頻率合成器系列。

PLL頻率合成器可以從多個(gè)基本構(gòu)建模塊的角度來考察�����。 我們?cè)谇懊嬉呀?jīng)提到過這個(gè)問題,下面將更加詳細(xì)地進(jìn)行探討:

鑒頻鑒相器(PFD)

參考計(jì)數(shù)器(R)

反饋計(jì)數(shù)器(N)

鑒頻鑒相器(PFD)

頻率合成器的核心是鑒相器����,也稱鑒頻鑒相器。 在鑒相器中��,將比較參考頻率信號(hào)與從VCO輸出端反饋回來的信號(hào)�����,結(jié)果得到的誤差信號(hào)用于驅(qū)動(dòng)環(huán)路濾波器和VCO�����。 在數(shù)字PLL (DPLL)中���,鑒相器或鑒頻鑒相器是一個(gè)邏輯元件�����。三種最常用的實(shí)現(xiàn)方法為:

異或(EXOR)柵極

J-K觸發(fā)器

數(shù)字鑒頻鑒相器

這里���,我們只考慮PFD,這也是ADF4110和ADF4210頻率合成器系列中使用的元件,因?yàn)榕cEXOR柵極和J-K觸發(fā)器不同���,處于解鎖狀態(tài)時(shí)����,其輸出為頻差以及兩個(gè)輸入間相差的函數(shù)����。

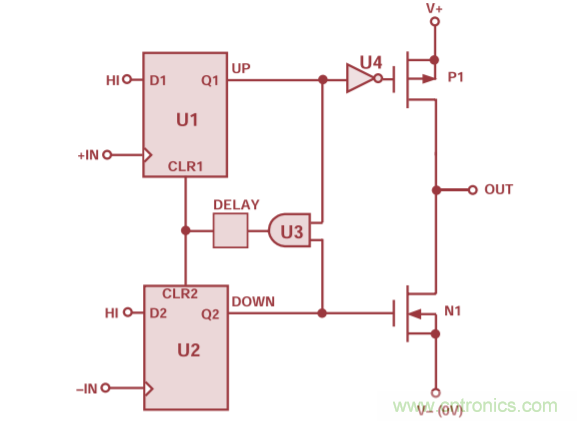

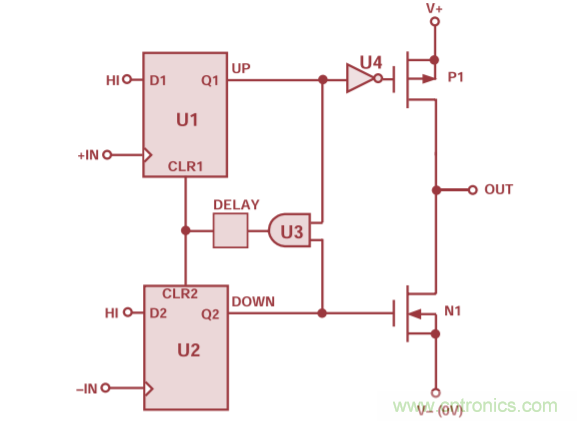

圖1所示為PFD的一種實(shí)現(xiàn)方案��,該類器件基本上由兩個(gè)D型觸發(fā)器組成����。 一路Q輸出使能正電流源,另一路Q輸出則使能負(fù)電流源��。 假設(shè)本設(shè)計(jì)中D型觸發(fā)器由正邊沿觸發(fā)�����,則狀態(tài)為(Q1, Q2):

11—兩個(gè)輸出均為高電平�����,由反饋至觸發(fā)器上CLR引腳的AND柵極(U3)禁用����。

00—P1和N1均關(guān)閉��,輸出OUT實(shí)際處于高阻抗?fàn)顟B(tài)��。

10—P1開啟��,N1關(guān)閉�����,輸出位于V+��。

01—P1關(guān)閉���,N1開啟,輸出位于V–��。

圖1. 運(yùn)用D型觸發(fā)器的典型PFD���。

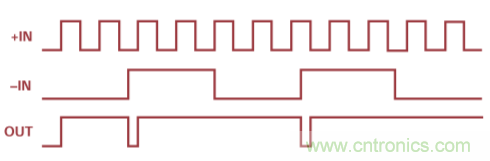

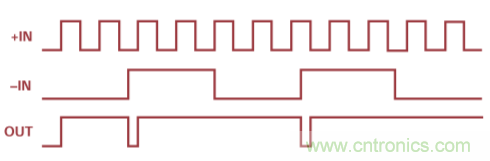

現(xiàn)在考慮系統(tǒng)失鎖且+IN處的頻率遠(yuǎn)高于–IN處的頻率時(shí)電路的性能表現(xiàn)����,如圖2所示。

圖2. PFD波形(鎖頻和鎖相均解除)�����。

由于+IN處的頻率遠(yuǎn)高于–IN處的頻率��,因此輸出多數(shù)時(shí)間處于高電平狀態(tài)���。 +IN上的第一個(gè)上升沿會(huì)發(fā)送輸出高電平�����,并且這種情況會(huì)一直持續(xù)到–IN上出現(xiàn)第一個(gè)上升沿。在實(shí)際的系統(tǒng)中�����,這就意味著輸出及VCO的輸入會(huì)被進(jìn)一步拉高��,進(jìn)而造成–IN處的頻率增加�����。這恰恰是期望達(dá)到的效果��。

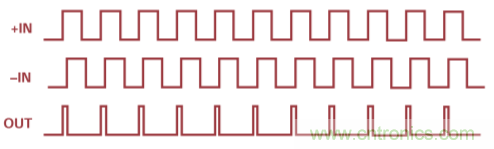

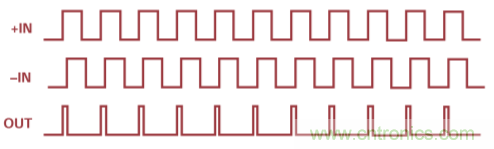

如果+IN處的頻率遠(yuǎn)低于–IN處的,則會(huì)出現(xiàn)相反效果����。 OUT處的輸出多數(shù)時(shí)間處于低電平狀態(tài)。 這會(huì)在負(fù)方向上驅(qū)動(dòng)VCO��,并再次使得–IN處的頻率更加接近+IN處的頻率��,從而達(dá)到鎖定條件�����。 圖3顯示了輸入處于鎖頻和接近鎖相條件時(shí)的波形��。

圖3. PFD波形(鎖頻�����,但相位鎖定解除)����。

由于+IN領(lǐng)先于–IN,因此輸出為一系列正電流脈沖���。 這些脈沖往往會(huì)驅(qū)動(dòng)VCO�����,使得–IN信號(hào)變得與+IN信號(hào)相位對(duì)齊�����。

發(fā)生這種情況時(shí)���,如果U3和U1及U2的CLR輸入端之間沒有任何延遲元件����,那么輸出可能會(huì)進(jìn)入高阻抗模式���,從而既不會(huì)生成正電流脈沖,也不會(huì)生成負(fù)電流脈沖���。 這并不是一種很好的狀況��。 VCO會(huì)發(fā)生漂移���,直到造成顯著的相位誤差并再次開始生成正電流脈沖或負(fù)電流脈沖。 這種循環(huán)會(huì)持續(xù)相當(dāng)長(zhǎng)的一段時(shí)間�����,其影響是電荷泵的輸出會(huì)被某個(gè)信號(hào)(PFD輸入?yún)⒖碱l率的次諧波)調(diào)制。 由于這可能是一種低頻信號(hào)�����,因此無法通過環(huán)路濾波器進(jìn)行衰減���,從而會(huì)導(dǎo)致VCO輸出頻譜中出現(xiàn)非常明顯的雜散���,該現(xiàn)象稱為“間隙”效應(yīng)。 通過在U3的輸出端和U1及U2的CLR輸入端之間添加延遲元件��,可以確保不會(huì)發(fā)生這種情況���。 添加延遲元件后�����,即使+IN和–IN相位完全對(duì)齊時(shí)��,電荷泵輸出端仍會(huì)生成電流脈沖�����。 該延遲的持續(xù)時(shí)間等于在U3輸出處插入的延遲�����,稱為反沖防回差脈沖寬度��。

參考計(jì)數(shù)器

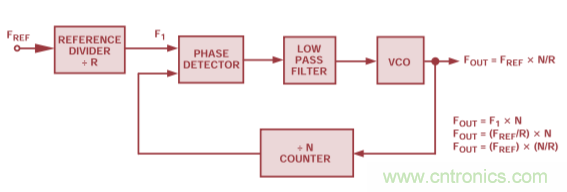

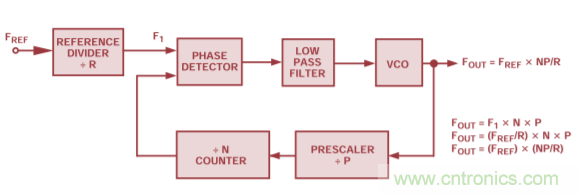

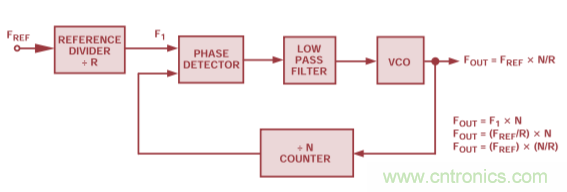

在傳統(tǒng)的整數(shù)N分頻頻率合成器中���,輸出頻率的分辨率由施加于鑒相器的參考頻率決定���。 因此,舉例來說����,如果需要200 kHz間距(如GSM電話中),那么參考頻率必須為200 kHz����。 但是��,獲取穩(wěn)定的200 kHz頻率源并不容易����。 一種合理的做法是采用基于晶振的良好高頻源并對(duì)其進(jìn)行分頻��。 例如��,從10 MHz頻率基準(zhǔn)開始并進(jìn)行50分頻����,就可以得到所需的頻率間隔����。這種方法如圖4所示。

圖4 在PLL頻率合成器中使用參考計(jì)數(shù)器�����。

反饋計(jì)數(shù)器N

N計(jì)數(shù)器也稱為N分頻器��,是用于設(shè)置PLL中輸入頻率和輸出頻率之間關(guān)系的可編程元件���。 N計(jì)數(shù)器的復(fù)雜性逐年增長(zhǎng)�����。 除簡(jiǎn)單的N計(jì)數(shù)器之外����,經(jīng)過發(fā)展,后來還包括“預(yù)分頻器”���,后者可具有“雙模”��。

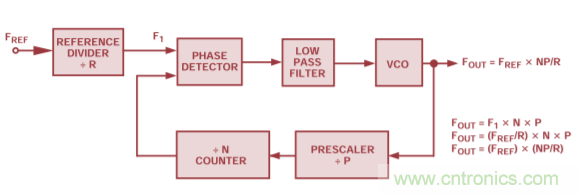

這種結(jié)構(gòu)已經(jīng)發(fā)展成為下列情況下固有問題的一種解決方案:需要超高頻輸出時(shí)使用基本N分頻結(jié)構(gòu)來反饋至鑒相器�����。 例如����,我們假設(shè)需要一個(gè)間距為10 Hz的900 MHz輸出���。 可以使用10 MHz參考頻率并將R分頻器設(shè)為1000���。然后,反饋中的N值必須為90,000���。這意味著����,至少需要一個(gè)能夠處理900 MHz輸入頻率的17位計(jì)數(shù)器�����。

為處理此范圍�����,需要考慮在可編程計(jì)數(shù)器之前加上一個(gè)固定計(jì)數(shù)器元件��,以便將超高輸入頻率拉低至標(biāo)準(zhǔn)CMOS的工作頻率范圍內(nèi)����。 該計(jì)數(shù)器稱為預(yù)分頻器,如圖5所示�����。

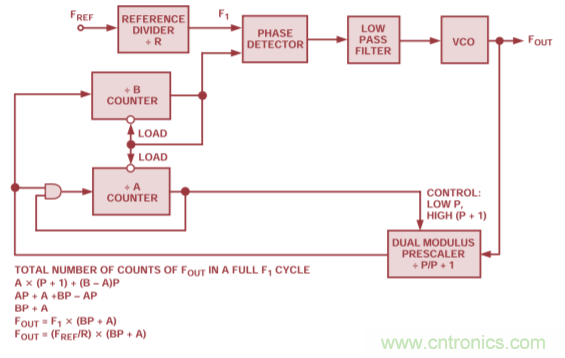

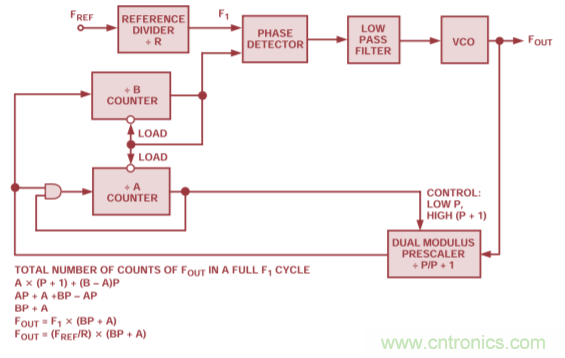

然而���,使用標(biāo)準(zhǔn)的預(yù)分頻器會(huì)導(dǎo)致其他并發(fā)癥���。 現(xiàn)在,系統(tǒng)分辨率降低(F1 × P)���。 可通過使用雙模預(yù)分頻器來解決這個(gè)問題(圖6)����。 這種方法可以享有標(biāo)準(zhǔn)預(yù)分頻器種種優(yōu)勢(shì),又不會(huì)犧牲系統(tǒng)分辨率�����。 雙模預(yù)分頻器是一種可通過外部控制信號(hào)將分頻比從一個(gè)值切換為另一個(gè)值的計(jì)數(shù)器���, 通過使用帶有A和B計(jì)數(shù)器的雙模預(yù)分頻器����,仍可以保持F1的輸出分辨率���。 不過���,必須滿足下列條件:

圖5. 基本預(yù)分頻器。

圖6. 雙模預(yù)分頻器��。

1.如果兩個(gè)計(jì)數(shù)器未超時(shí)����,其輸出信號(hào)都為高電平���。

2.當(dāng)B計(jì)數(shù)器超時(shí)時(shí),其輸出變?yōu)榈碗娖?��,并立即將兩個(gè)計(jì)數(shù)器加載至其預(yù)設(shè)值。

3.加載到B計(jì)數(shù)器的值必須始終大于加載到A計(jì)數(shù)器的值����。

假設(shè)B計(jì)數(shù)器剛發(fā)生超時(shí)并且兩個(gè)計(jì)數(shù)器均已經(jīng)重新加載值A(chǔ)和B。我們來看看再次達(dá)到相同狀態(tài)所需的VCO周期數(shù)��。

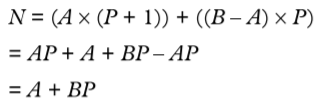

只要A計(jì)數(shù)器未超時(shí)���,預(yù)分頻器即會(huì)以P + 1進(jìn)行分頻�����。因此���,每次預(yù)分頻器計(jì)數(shù)達(dá)到(P + 1)個(gè)VCO周期時(shí),A和B計(jì)數(shù)器都會(huì)遞減1���。 這意味著��,A計(jì)數(shù)器會(huì)在((P + 1) × A)個(gè)VCO周期后超時(shí)�����。 然后��,預(yù)分頻器會(huì)切換至P分頻��。也可以說����,此時(shí)B計(jì)數(shù)器還有(B – A)個(gè)周期才會(huì)超時(shí)。 所需時(shí)間為: ((B – A) × P)�����。 現(xiàn)在��,系統(tǒng)會(huì)返回到剛開始的初始條件����。

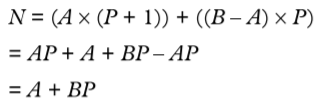

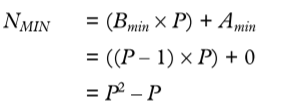

所需的VCO周期總數(shù)為:

在使用雙模預(yù)分頻器時(shí),必須考慮N的最低值和最高值�����。這里,我們真正想要的是可以按離散整數(shù)步長(zhǎng)更改N的范圍���?��?紤]表達(dá)式N = A + BP。為確保N有連續(xù)的整數(shù)間距����,A必須在0至(P – 1)之間���。這樣���,每當(dāng)B遞增時(shí),就有充足的分辨率來填充BP 和(B + 1)P之間的所有整數(shù)值���。

就如我們針對(duì)雙模預(yù)分頻器提到的那樣���,B必須大于或等于A,雙模預(yù)分頻器才能正常工作�����。基于此���,我們可以說���,若要按離散整數(shù)步長(zhǎng)遞增,最小分頻比為:

N 的最高值來自

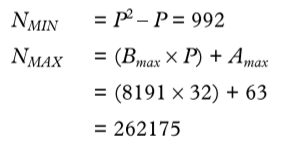

本例中����,Amax 和Bmax僅僅取決于A和B計(jì)數(shù)器的大小。接下來��,我們將給出一個(gè)采用ADF4111的例子����。

我們假設(shè),通過編程將預(yù)分頻器的分頻比設(shè)為32/33���。

A計(jì)數(shù)器: 6位意味著��,A可能為26– 1 = 63

B計(jì)數(shù)器: 13位意味著�����,B可能為213 – 1 = 8191

ADF4110系列

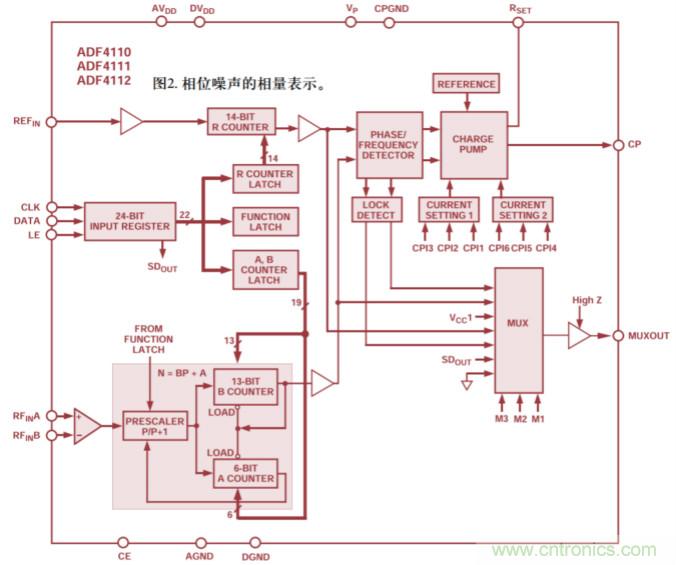

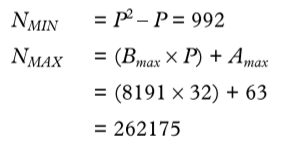

前面幾節(jié)討論的構(gòu)建模塊在來自ADI公司的新型整數(shù)N頻率合成器系列中均有使用���。ADF4110系列頻率合成器由單個(gè)器件構(gòu)成�����,ADF4210系列由雙通道版本構(gòu)成���。ADF4110的框圖如下所示。其中含有上面描述的參考計(jì)數(shù)器�����、雙模預(yù)分頻器����、N計(jì)數(shù)器和PFD模塊��。

圖7. ADF4110系列的框圖��。

小數(shù)N頻率合成器s*

許多新興無線通信系統(tǒng)都要求本振(LO)具有更快的切換能力和更低相位噪聲�����。整數(shù)N頻率合成器要求參考頻率等于通道間距����。該值可能非常低����,意味著高N����。該高N會(huì)產(chǎn)生相應(yīng)較高的相位噪聲。低參考頻率會(huì)限制PLL鎖定時(shí)間����。小數(shù)N合成是在PLL中同時(shí)實(shí)現(xiàn)低相位噪聲和快速鎖定時(shí)間的一種方式。

這種技術(shù)最初出現(xiàn)在20世紀(jì)70年代初��。早期工作主要由惠普公司和Racal公司完成����。該技術(shù)最初稱為“digiphase”,但后來被廣泛稱為小數(shù)N�����。

在標(biāo)準(zhǔn)頻率合成器中��,只能用一個(gè)整數(shù)除以RF信號(hào)���。這就需要使用一個(gè)相對(duì)較低的參考頻率(取決于系統(tǒng)通道間距)����,并在反饋中導(dǎo)致高N值。這兩個(gè)事實(shí)都對(duì)系統(tǒng)建立時(shí)間和系統(tǒng)相位噪聲有著重要影響�����。低參考頻率意味著較長(zhǎng)的建立時(shí)間����,高N值意味著較大的相位噪聲。

如果反饋中可能出現(xiàn)除數(shù)為小數(shù)的情況���,則可以使用較高的參考頻率��,同時(shí)實(shí)現(xiàn)通道間距目標(biāo)。小數(shù)越小���,則意味著相位噪聲越低���。

事實(shí)上,通過交替除以兩個(gè)整數(shù)�����,可以實(shí)現(xiàn)在較長(zhǎng)時(shí)間內(nèi)用小數(shù)除(通過先后除以2和3可以除以2.5)。

那么�����,如何除以X或(X + 1)(假設(shè)小數(shù)在這兩個(gè)值之間)����? 數(shù)值的小數(shù)部分可以按參考頻率速率累加。

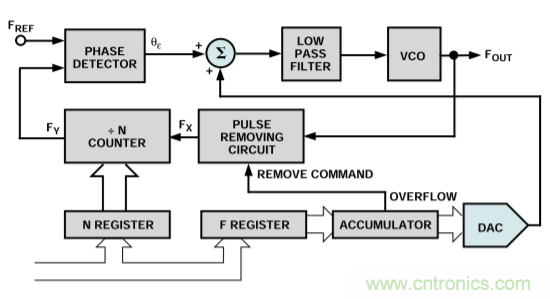

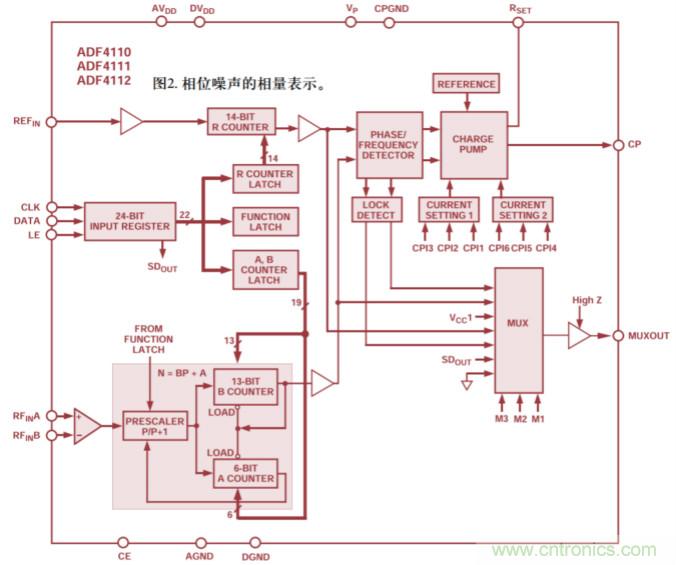

圖8. 小數(shù)N頻率合成器���。

然后�����,每當(dāng)累加器溢出時(shí)����,就可以用該信號(hào)來更改N分頻比�����。在圖8中,這是通過移除饋入N計(jì)數(shù)器的一個(gè)脈沖來實(shí)現(xiàn)的����。實(shí)際上,每當(dāng)累加器溢出時(shí)��,結(jié)果會(huì)使分頻比加1����。另外,F(xiàn)寄存器中的數(shù)值越大��,累加器溢出次數(shù)越多��,以較大數(shù)值為除數(shù)的次數(shù)也就越多����。這正是電路的目的所在。但會(huì)增加一些并發(fā)癥���。從N分頻電路饋入鑒相器的信號(hào)在實(shí)時(shí)表現(xiàn)上并不均勻��。相反,其調(diào)制速率取決于參考頻率和編程小數(shù)��。結(jié)果又調(diào)制鑒相器輸出,并進(jìn)入VCO輸入端��。最后����,在VCO輸出端會(huì)出現(xiàn)較多的雜散內(nèi)容。目前業(yè)界正在努力解決這些雜散問題���。 一種方法是采用DAC����,如圖8所示���。

目前為止���,單芯片小數(shù)N頻率合成器仍然未能達(dá)到預(yù)期,但最終可以實(shí)現(xiàn)的效益意味著����,其發(fā)展正在快馬加鞭地進(jìn)行。

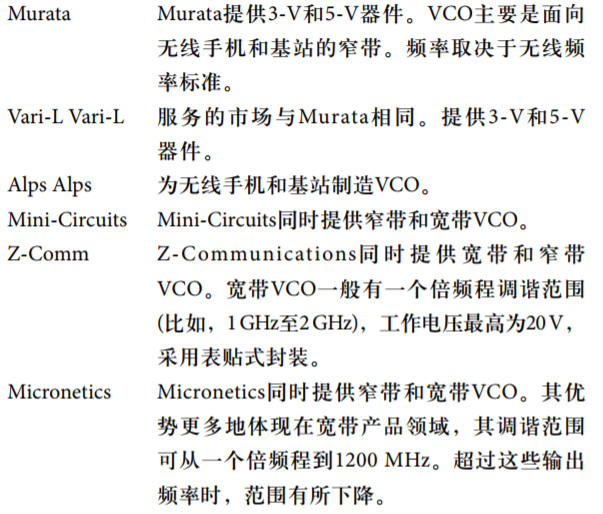

VCO制造商小結(jié)

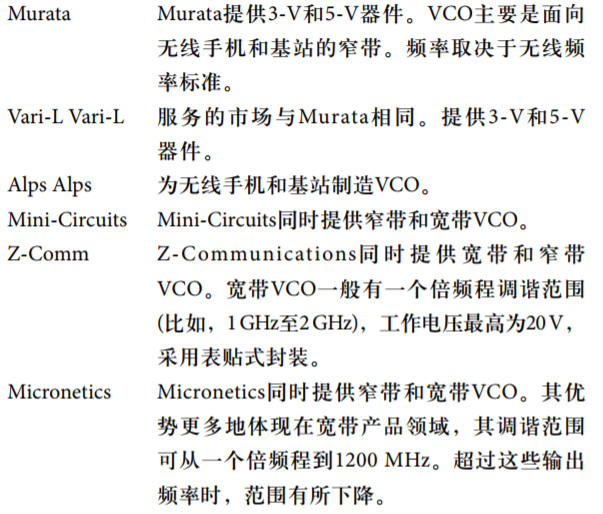

在過去5年中���,隨著無線通信的爆炸式增長(zhǎng)�����,對(duì)頻率合成器����、VCO等產(chǎn)品的需求也出現(xiàn)了大幅增長(zhǎng)。 有意思的是�����,到目前為止����,為市場(chǎng)提供服務(wù)的制造商分為涇渭分明的兩個(gè)陣營(yíng)。 以下列出了VCO領(lǐng)域的部分制造商���。 列表并未窮盡所有制造商��,只是讓讀者獲得對(duì)一些主要參與者的認(rèn)識(shí)��。

VCO

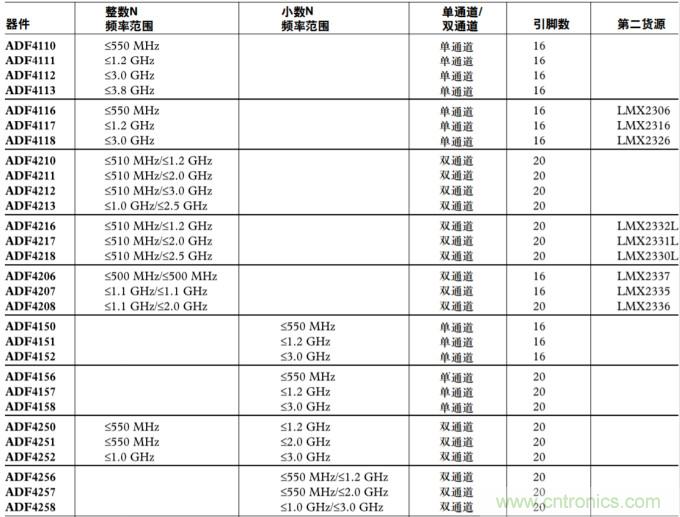

ADI頻率合成器系列

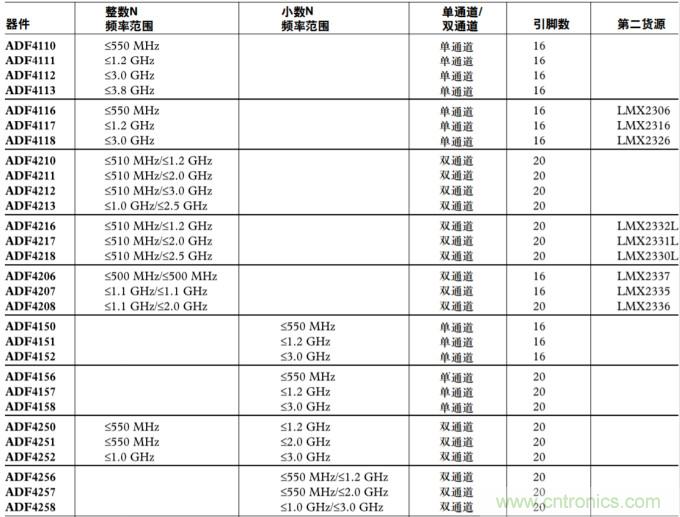

下表列出了ADF4xxx頻率合成器系列的未來成員����, 其中包括單通道和雙通道器件�����,以及整數(shù)N和小數(shù)N器件���。

致謝

ADF4xxx系列頻率合成器在愛爾蘭利默里克的ADI工廠中設(shè)計(jì)���。 產(chǎn)品線團(tuán)隊(duì)包括: Mike Tuthill、Leo McHugh����、Bill Hunt、Mike Keaveney���、Brendan Daly��、Paul O’Brien��、Paul Mallon����、Ian Collins�����、Sinead O’Keefe、Liam McCann���、Patrick Walsh�����、Cristoir O’Reilly����、Paul Laven���、Samuel Landete�����、Niall Kearney和Mike Curtin���。 團(tuán)隊(duì)希望借此機(jī)會(huì)向ADI公司英國(guó)肯特分公司的Jon Strange和Ashish Shah,以及ADI公司西北實(shí)驗(yàn)室(美國(guó)俄勒岡州比佛頓)的Fred Weiss致以誠摯的謝意��,感謝他們提出的寶貴意見��。

參考文獻(xiàn)

1. Mini-Circuits Corporation, VCO Designer’s Handbook, 1996.

Mini-Circuits公司�����,VCO Designer’s Handbook(VCO設(shè)計(jì)師手冊(cè)),1996年�����。

2. L.W. Couch, Digital and Analog Communications Systems, Macmillan Publishing Company, New York, 1990.

L.W. Couch����,Digital and Analog Communications Systems(數(shù)字與模擬通信系統(tǒng))����,Macmillan Publishing Company,New York���,1990年�����。

3. P. Vizmuller, RF Design Guide, Artech House, 1995.

P. Vizmuller����,RF Design Guide(RF設(shè)計(jì)指南)��,Artech House,1995年�����。

4. R.L. Best, Phase Locked Loops: Design, Simulation and Applications, 3rd Edition, McGraw-Hill, 1997.

R.L. Best�����,Phase Locked Loops: Design, Simulation and Applications(鎖相環(huán):設(shè)計(jì)��、仿真與應(yīng)用)����,第3版,McGraw-Hill����,1997年。

免責(zé)聲明:本文為轉(zhuǎn)載文章���,轉(zhuǎn)載此文目的在于傳遞更多信息�����,版權(quán)歸原作者所有��。本文所用視頻�����、圖片�����、文字如涉及作品版權(quán)問題�����,請(qǐng)聯(lián)系小編進(jìn)行處理�����。

推薦閱讀: