【導(dǎo)讀】高速先生前面零零散散的寫了一些DDR3系列的文章,雖然有小部分的案例說到了問題點,但那只是為了引出主題而寫,而且只是點到為止,既然是案例,就要把問題的來龍去脈描述清楚,這個案例的問題是這樣的:

某客戶有一個板子需要新增一部分功能,想將原來的小板改為大板,但出于成本考慮,又將原來的8層板改為了6層板,板子做出來后在實際測試時DDR3只能降頻到400MHz才能穩(wěn)定工作,而之前的8層板可以穩(wěn)定工作在533MHz,這兩版的電源供給情況基本一致,主控及DDR3芯片的型號和批次也是一致的。客戶也是比較有經(jīng)驗的,做過多種嘗試如調(diào)整驅(qū)動及ODT等都沒有改善,后來就找到了我們。

原因分析:大家都知道,一般DDR3運行不到額定的頻率最直接的影響因素就是時序,時序裕量太小或不足都會導(dǎo)致系統(tǒng)工作不穩(wěn)定或根本就運行不上去。而影響DDR3時序的因素主要有以下幾點:電源噪聲、串?dāng)_、等長匹配、信號質(zhì)量等。只要上面幾大點沒出什么問題,DDR3出問題的幾率也會相對少很多(前提是硬件原理和軟件配置沒問題)。下面我們就針對各種因素來各個擊破,這種時候用排除法是比較好的。

電源噪聲:電容分布基本上是0.1uF的電容,無其他容值的電容,適當(dāng)增加幾個大容值電容在低頻的時候效果更好,但測試電源噪聲只有20mV左右,量級比較小,所以電源噪聲的影響可以初步排除。

串?dāng)_問題:數(shù)據(jù)信號間距10.55mil,地址信號10mil;信號之間的間距為2H(W),線路中心距離為3H(W),若空間允許,間距可以適當(dāng)加大。

信號與旁邊的電源地網(wǎng)絡(luò)不能太近,需要避免(小問題)

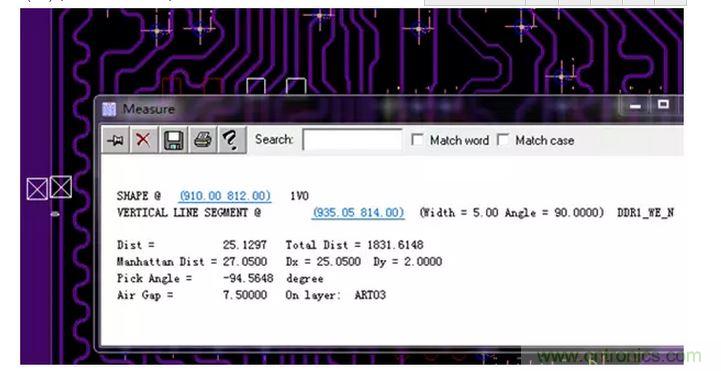

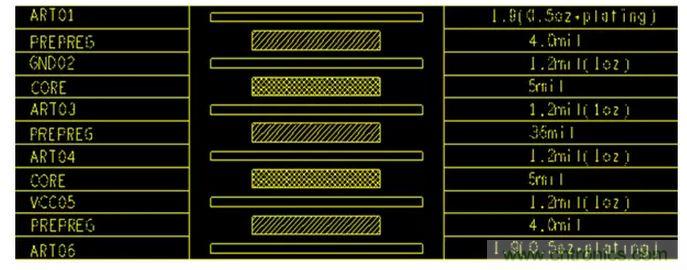

由于是3、4層內(nèi)層走線,但從疊層看3、4層之間的間距已足夠大,串?dāng)_問題影響比較小。

信號質(zhì)量問題:此板DDR3地址、命令信號用了外部的上拉電阻,另外客戶也已經(jīng)調(diào)整過芯片驅(qū)動及ODT功能,所以信號質(zhì)量問題也不大。

等長匹配問題:

1、主控芯片是否有write and read leveling(讀寫平衡)。經(jīng)查此主控芯片為國內(nèi)芯片廠家研發(fā)的,一般國產(chǎn)芯片需要格外注意,由于讀寫平衡功能需要購買額外的IP,而注重成本的國產(chǎn)芯片為了降低成本,結(jié)果就可想而知了,具備此功能的芯片就相對的比較少了。那沒有了這個功能,我們的DDR3通常就按照DDR2的約束規(guī)則來布線(就事論事,沒有貶低國產(chǎn)芯片的意思,事實上我們都要支持國產(chǎn)哈,支持國產(chǎn),從你我做起,希望國貨越來越強?。?/div>

2、重點關(guān)注數(shù)據(jù)組與時鐘(地址)的等長匹配。

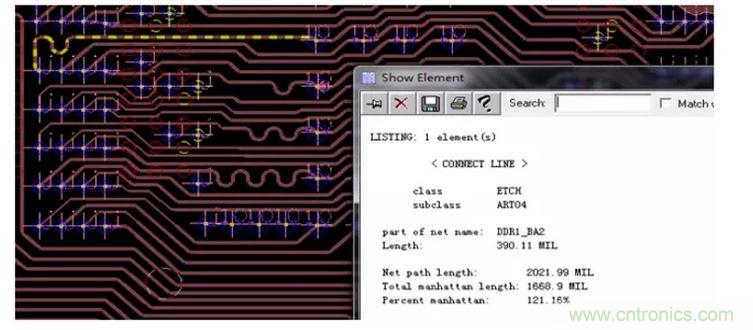

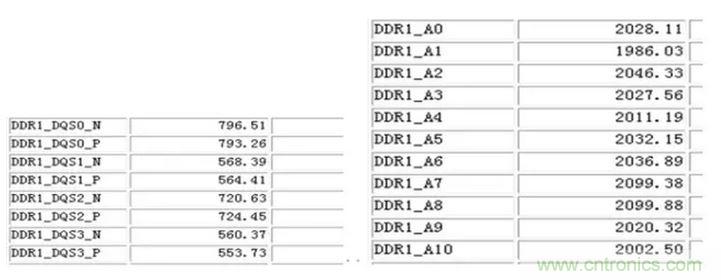

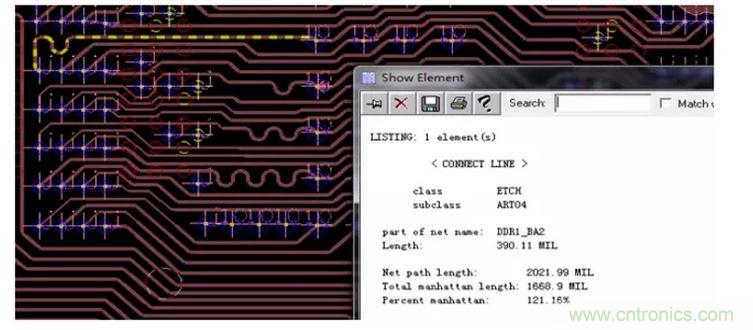

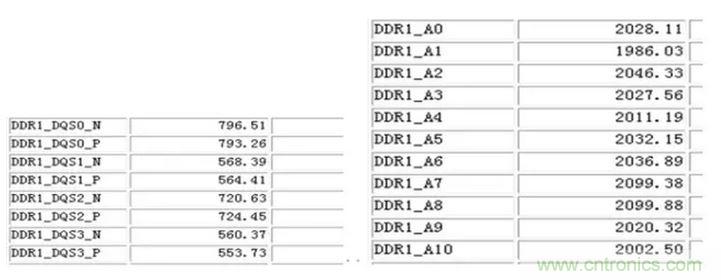

正常工作的板子走線長度如下所示,地址與時鐘的長度相差200mil內(nèi):

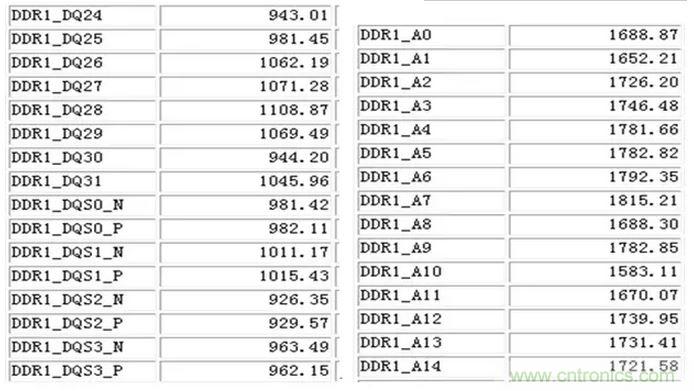

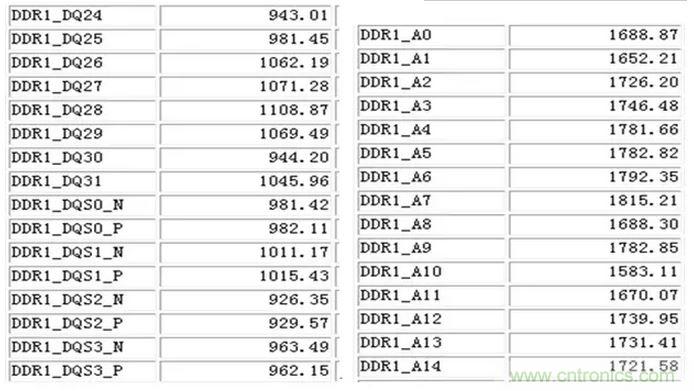

有欠缺的板子走線長度如下所示。

•數(shù)據(jù)組內(nèi)做了嚴格等長,地址、控制、時鐘也做了等長,但數(shù)據(jù)與時鐘相差較大,如下所示。

•地址信號平均總長度2000mil減掉一個分支長度400mil,大致可以知道主控到其中一個顆粒的長度在1600mil,而數(shù)據(jù)信號最短的長度才550mil,之間相差比較大,超過了1000mil。

這也是前后兩版差異最大的地方,由于主控芯片沒有讀寫平衡功能,再加上由之前的8層板改成了6層板,布線空間的減少就使得我們的工程師沒有過多的去繞線,而系統(tǒng)不能自動調(diào)整數(shù)據(jù)與時鐘的偏差,最終導(dǎo)致時序裕量不夠,這應(yīng)該就是DDR3運行不到額定頻率的主要原因。