【導(dǎo)讀】本文介紹電源工程師必須具備的設(shè)計(jì)技巧���,即如何解決電磁干擾問題��,避免EMI性能被毀掉�。在開關(guān)電源研發(fā)設(shè)計(jì)中,從開關(guān)節(jié)點(diǎn)到輸入引線的少量寄生電容(100毫微微法拉)����,會(huì)讓你無法滿足電磁干擾(EMI)需求�。怎么辦呢�����?

一般情況下�����,100fF電容器不多��。即使有��,它們也會(huì)因寄生問題而提供寬泛的容差�����。不過在你的電源中很容易找到作為寄生元件的100fF電容器���。只有處理好它們才能獲得符合EMI標(biāo)準(zhǔn)的電源。

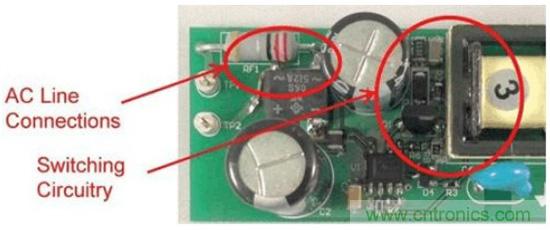

圖1是這些非計(jì)劃中電容的一個(gè)實(shí)例����。圖中的右側(cè)是一個(gè)垂直安裝的FET,所帶的開關(guān)節(jié)點(diǎn)與鉗位電路延伸至了圖片的頂部。輸入連接從左側(cè)進(jìn)入����,到達(dá)距漏極連接1cm以內(nèi)的位置。這就是故障點(diǎn)����,在這里FET的開關(guān)電壓波形可以繞過EMI濾波器耦合至輸入。

圖1:開關(guān)節(jié)點(diǎn)與輸入連接臨近����,會(huì)降低EMI性能

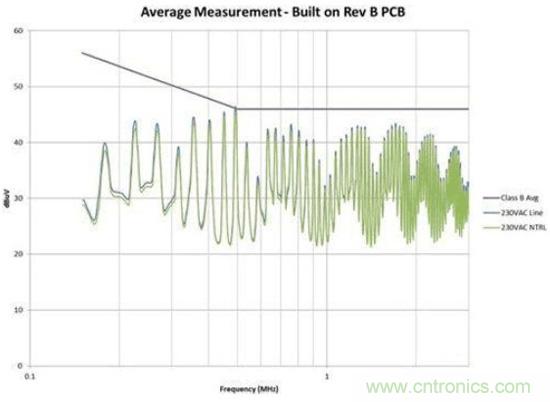

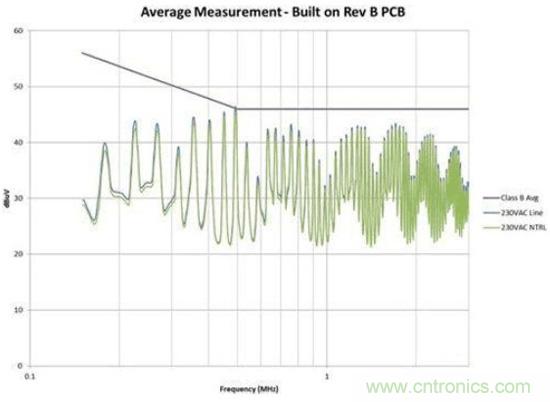

注意,漏極連接與輸入引線之間有一些由輸入電容器提供的屏蔽��。該電容器的外殼連接至主接地�����,可為共模電流提供返回主接地的路徑��。如圖2所示���,這個(gè)微小的電容會(huì)導(dǎo)致電源EMI簽名超出規(guī)范要求���。

圖2:寄生漏極電容導(dǎo)致超出規(guī)范要求的EMI性能

這是一條令人關(guān)注的曲線����,因?yàn)樗从吵隽藥讉€(gè)問題:明顯超出了規(guī)范要求的較低頻率輻射���、共模問題通常很明顯的1MHz至2MHz組件�����,以及較高頻率組件的衰減正弦(x)/x分布����。需要采取措施讓輻射不超出規(guī)范�����。我們利用通用電容公式將其降低了:C=ε˙A/d����。

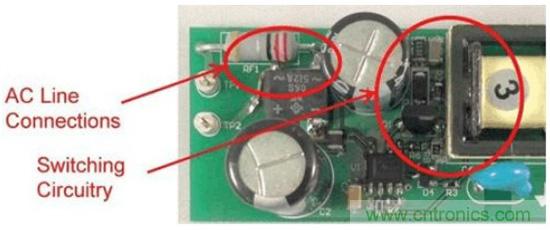

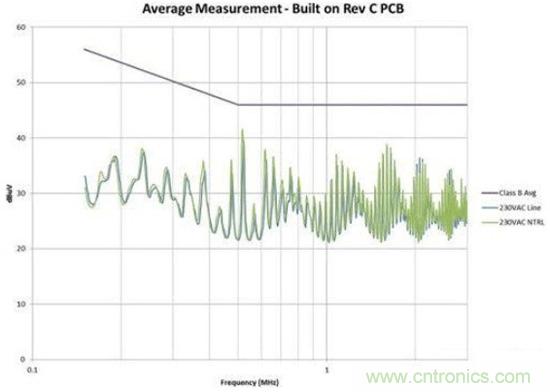

我們無法改變電容率(ε)�,而且面積(A)也已經(jīng)是最小的了。不過����,我們可以改變間距(d)。如圖3所示,我們將組件與輸入的距離延長(zhǎng)了3倍���。最后�����,我們采用較大接地層增加了屏蔽�����。

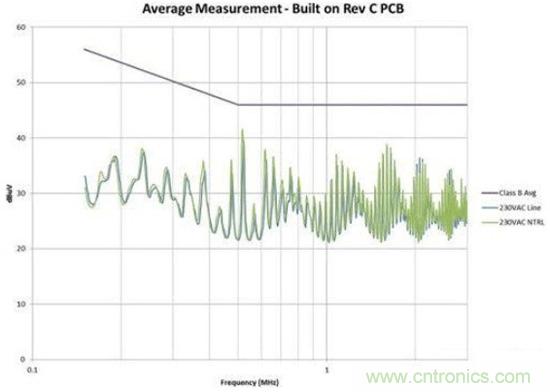

圖3:修改后的布局可增加間距�����,且還可帶來屏蔽性能

圖4是修改后的效果圖����。我們?cè)诠收宵c(diǎn)位置為EMI規(guī)范獲得了大約6dB的裕量�����。此外�����,我們還顯著減少了總體EMI簽名。所有這些改善都僅僅是因?yàn)椴季值恼{(diào)整��,并未改變電路���。如果您的電路具有高電壓開關(guān)并使用了屏蔽距離�����,您需要非常小心地對(duì)其進(jìn)行控制��。

圖4:EMI性能通過屏蔽及增加的間距得到了改善

由上述實(shí)例我們可以總結(jié)出來自離線開關(guān)電源開關(guān)節(jié)點(diǎn)的100fF電容會(huì)導(dǎo)致超出規(guī)范要求的EMI簽名��。這種電容量只需寄生元件便可輕松實(shí)現(xiàn)�����,例如對(duì)漏極連接進(jìn)行路由,使其靠近輸入引線����。通常可通過改善間距或屏蔽來解決該問題��。要想獲得更大衰減�����,需要增加濾波或減緩電路波形。