【導(dǎo)讀】本系統(tǒng)以MSP430為控制核心設(shè)計(jì)并制作一個(gè)正弦波和脈沖波信號源。本實(shí)驗(yàn)分為四大模塊,分別是鍵盤掃描模塊,正弦波產(chǎn)生模塊,脈沖波產(chǎn)生模塊和液晶顯示模塊。

正弦產(chǎn)生部分采用DDS芯片AD9851產(chǎn)生頻率可控的正弦波,在實(shí)踐測試中得之從AD9851輸出的正弦波幅值會(huì)隨頻率變化,最后通過軟件編程明顯減少了幅值誤差。脈沖產(chǎn)生部分采用Verilog編程在FPGA內(nèi)部產(chǎn)生占空比可調(diào)的脈沖波,解決了由將正弦波變成方波再送FPGA產(chǎn)生脈沖波的不穩(wěn)定性。本系統(tǒng)工作可靠穩(wěn)定,較好地完成了基本部分和發(fā)揮部分的要求。

一. 總體方案

本系統(tǒng)要求在給定±15V電源電壓條件下設(shè)計(jì)出一個(gè)能產(chǎn)生正波和脈沖波的信號源。信號頻率為20Hz~20kHz,頻率能程控步進(jìn)調(diào)整(步長為5Hz),脈沖波的占空比在2%~98%之間能程控步進(jìn)調(diào)整(步長2%),兩路信號均要求幅值在100mv到3V步進(jìn)可調(diào)(步長為100mv),要求性能良好(頻率穩(wěn)度高,非線性失真小等),方案考慮如下:

正弦波產(chǎn)生

方案一:采用單片函數(shù)信號發(fā)生器(如8038),8038可同時(shí)產(chǎn)生正弦波。脈沖波,方法簡單易行,用D/A轉(zhuǎn)換器的輸出來改變調(diào)制電壓,可以實(shí)現(xiàn)數(shù)控調(diào)整頻率,但步長難以滿足要求,且頻率穩(wěn)定度不高。

方案二:采用鎖相式頻率合成器,利用鎖相環(huán),將壓控振蕩器(vco)的輸出頻率鎖定在所需頻率上,該方案性能良好,但難以達(dá)到輸出頻率覆蓋系數(shù)的要求,且電路復(fù)雜,不適于產(chǎn)生低頻信號。

方案三:采用直接數(shù)字頻率合成芯片AB9851,可以很方便地生成正弦波和脈沖波。DDS特別適合于生成頻率低、頻帶寬、頻率穩(wěn)定性和準(zhǔn)確度較高及波形復(fù)雜的場合。

脈沖波產(chǎn)生

方案一:由D/A轉(zhuǎn)換器產(chǎn)生占空比相應(yīng)的電壓,將之與正弦信號進(jìn)行比較就可得到所需占空比方波。但這種方法精度較差,難以達(dá)到2%的步進(jìn)要求。

方案二:先把正弦波變換為鋸齒波或三角波,然后進(jìn)行比較。這樣一來雖然可以提高精度,但電路復(fù)雜,成本高,調(diào)試也困難。

方案三:采用計(jì)數(shù)定時(shí)方法,先將正弦波變換為方波送入FPGA,再用它的上升沿觸發(fā)一計(jì)時(shí)電路,該電路在計(jì)時(shí)期間輸出為高電平,計(jì)時(shí)終止后輸出為低電平, 從而實(shí)現(xiàn)脈沖波的占空比步進(jìn)可調(diào),占空比由單片機(jī)傳輸給FPGA。此方案構(gòu)成的兩模塊有影響,形成信號源不穩(wěn)定。

方案四:在單片機(jī)MSP430的控制下,通過軟件編程直接在FPGA內(nèi)部產(chǎn)生可控占空比脈沖波,實(shí)現(xiàn)比較容易,產(chǎn)生信號源十分穩(wěn)定。

根據(jù)以上分析,選用如下方案:

(1)正弦波采用DDS芯片AD9851用動(dòng)態(tài)生成程序的方法來實(shí)現(xiàn)。

(2)方波的產(chǎn)生方波由編程在FPGA內(nèi)部生成。

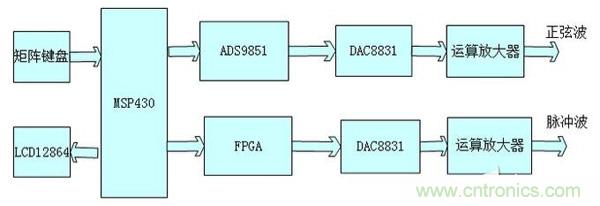

信號源系統(tǒng)的原理框圖如圖所示:

圖1.系統(tǒng)總體框圖

二. 系統(tǒng)設(shè)計(jì)

2.1 硬件設(shè)計(jì)

2.1.1 正弦波產(chǎn)生電路

DDS單片頻率合成器AD9851的ROM中已預(yù)先存入正弦函數(shù)表,其幅度按二進(jìn)制分辨率量化,其相位一個(gè)周期360o按2∏/232的分辨率設(shè)立相位取樣點(diǎn)。然后存入ROM相應(yīng)地址中。工作時(shí),用單片機(jī)送入頻率碼。輸入采用并行方式,8位一個(gè)字節(jié),分5次輸入,其中32位是頻率碼,另8位中的5位是初始相伴控制碼,3位是掉電控制碼。改變讀取ROM的數(shù)目,即可改變輸出頻率。

輸出頻率的一般表達(dá)式為 fout=kfc/232

式中,k為頻率碼,是個(gè)32位的二進(jìn)制數(shù)。fc為系統(tǒng)時(shí)鐘頻率,即25MHz。

頻率變化范圍為20Hz~20kHz,周期變化范圍為50ms~50us。時(shí)鐘周期Tc=0.04us.當(dāng)輸出頻率最高,即fomax=20 kHz,則Tomin=50us,

步進(jìn)寬度為: △T=Tomin×2%=50×2%=1us

圖2

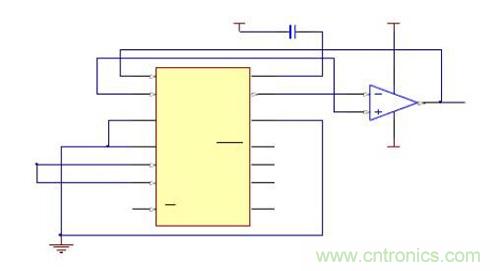

2.1.2 正弦波幅值可調(diào)電路

采用16位串行DA器件DAC8831來實(shí)現(xiàn)正弦波的幅度步進(jìn)。將DDS生成的正弦波接到DAC8831的基準(zhǔn)輸入端,通過單片機(jī)調(diào)整DA輸入數(shù)字量,從而完成正弦波100mv的步進(jìn)和幅值預(yù)置。

圖3

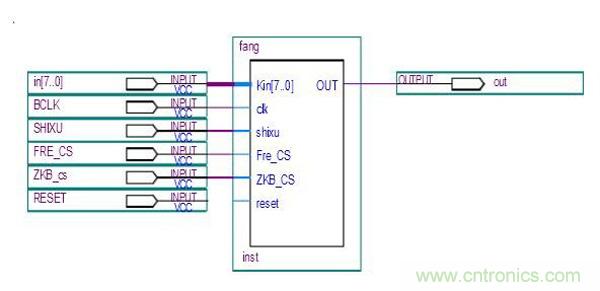

2.1.3 脈沖波形成電路

在單片機(jī)的控制下通過verilog編程在FPGA內(nèi)部產(chǎn)生可控脈沖波。

圖4

2.1.4 脈沖波幅值步進(jìn)調(diào)整電路:

本部分采用16串行DA器件DAC8831,接口簡單,且精度較高。電路圖與圖3-2相同。

2.2 軟件設(shè)計(jì)

2.2.1 基本思路

單片機(jī)控制AD9851產(chǎn)生頻率和相位都可控的正弦波,頻率量由鍵盤設(shè)定,步進(jìn)量為5Hz,AD9851頻率分辨率為0.006985Hz,完全能夠滿足要求。正弦信號送入DAC8831的基準(zhǔn)輸入端,單片機(jī)控制DA的數(shù)字量調(diào)節(jié)其幅值,設(shè)置按鍵調(diào)整幅值可實(shí)現(xiàn)100mv的步進(jìn)。在單片機(jī)的控制下編程在FPGA內(nèi)部產(chǎn)生占空比可調(diào)的脈沖波,單片機(jī)向FPGA送入占空比值和頻率值,F(xiàn)PGA通過計(jì)數(shù)值從而改變輸出脈沖波的占空比和頻率,設(shè)置按鍵調(diào)整占空比和幅值。正弦信號送入DAC8831的基準(zhǔn)輸入端,單片機(jī)控制DA的數(shù)字量調(diào)節(jié)其幅值,設(shè)置按鍵調(diào)整幅值可實(shí)現(xiàn)100mv的步進(jìn)。

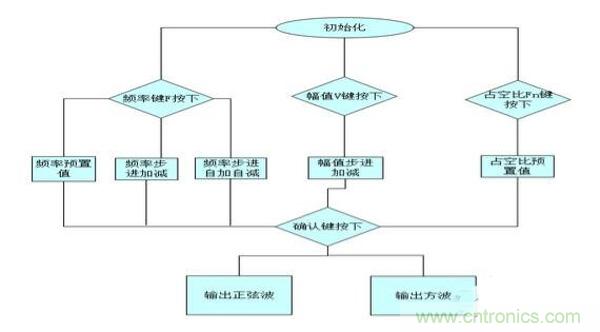

2.2.2 軟件流程圖

圖5.軟件流程圖

三、測試結(jié)果與分析

3.1 正弦波測試結(jié)果

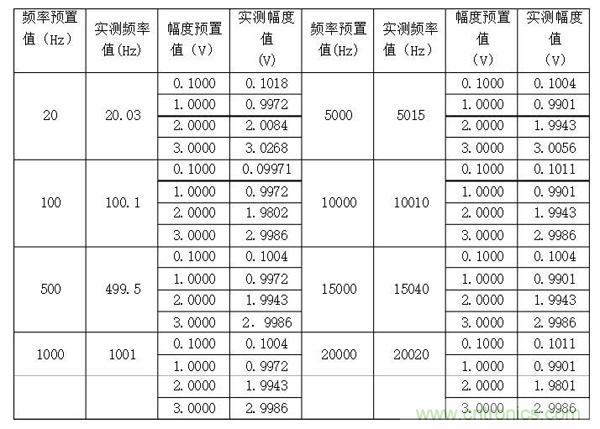

表一:

圖6

3.2 脈沖波測試結(jié)果

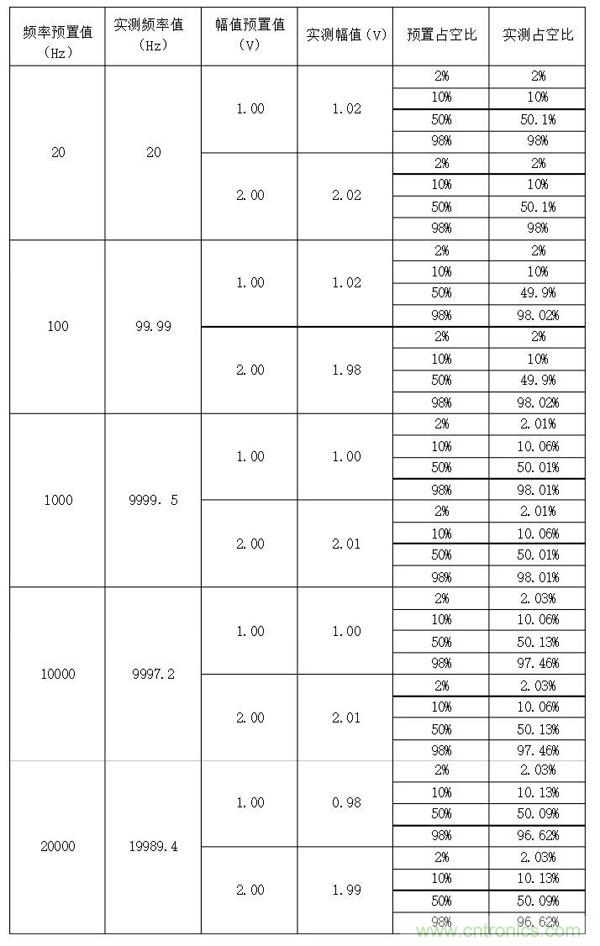

表二:

圖7

3.3 相對誤差統(tǒng)計(jì)

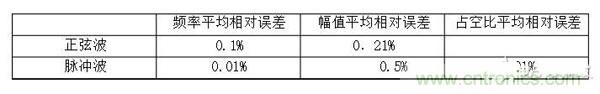

表三:

圖8

3.4 誤差分析

(1)DAC8831的量化誤差 DAC8831為16串行輸入的D/A轉(zhuǎn)化器,會(huì)引入一定的誤差。

(2)由于條件有限,采用手工焊接電路影響了整個(gè)電路的布局與走線,從而引入了一定的噪聲與干擾。

四、總結(jié)

在實(shí)現(xiàn)此項(xiàng)項(xiàng)目過程中,很快實(shí)現(xiàn)了對于產(chǎn)生可控的正弦波并在液晶上顯示的基本要求與發(fā)揮部分,DDS芯片AD9851產(chǎn)生頻率可控的正弦波,在實(shí)踐測試中得之從AD9851輸出的正弦波幅值會(huì)隨頻率變化,最后通過軟件編程明顯減少了幅值誤差。關(guān)鍵部分就在于產(chǎn)生占空比可控的脈沖波,起初的思路是由AD9851產(chǎn)生的正弦波經(jīng)過滯回比較器生成方波送到FPGA產(chǎn)生可控的脈沖波,但最后產(chǎn)生的脈沖波頻率與正弦波頻率不對應(yīng)且影響正弦波的穩(wěn)定度,兩個(gè)模塊之間有影響,最后討論改變方案,在MSP430送入控制信號的前提下在FPGA內(nèi)部產(chǎn)生可控的脈沖波,結(jié)果很理想,基本達(dá)到了實(shí)驗(yàn)要求和發(fā)揮的部分。