【導讀】半導體市場的最新趨勢是廣泛采用碳化硅(SiC)器件,包括用于工業(yè)和汽車應用的肖特基勢壘二極管(SBD)和功率MOSFET。與此同時,由于可供分析的現(xiàn)場數(shù)據(jù)有限,這些器件的長期可靠性成為一個需要解決的熱點問題。一些SiC供應商已開始根據(jù)嚴格的工業(yè)和汽車(AEC-Q101)標準來認證SiC器件,而另一些供應商不但超出了這些認證標準的要求,還能為惡劣環(huán)境耐受性測試提供數(shù)據(jù)。為了使SiC器件在任務和安全關(guān)鍵型應用中保持較高的普及率,應將這種認證和測試策略與特定的設計規(guī)則相結(jié)合來實現(xiàn)高雪崩耐受性,這一點至關(guān)重要。

市場快速增長

SiC器件的市場份額預計將在未來幾年加速增長,主要推動因素是運輸行業(yè)的電氣化。SiC管芯將成為車載充電器和動力傳動牽引系統(tǒng)等應用的模塊中的基本構(gòu)件。由于雪崩擊穿的臨界電場較高,因此高壓SiC器件的外形比同類硅器件小得多,并且可以在更高的開關(guān)頻率下工作。SiC的熱性能也十分出色,它不但擁有良好的散熱性能,還能在高溫下工作。實際上,最高工作溫度通常可達175 °C,很少超過200 °C,主要限制為裝配工藝(焊接金屬和封裝材料)。SiC器件本質(zhì)上比硅器件更高效,切換到SiC管芯可以極大減少模塊中單個管芯的數(shù)量。

隨著SiC器件從利基市場轉(zhuǎn)向主流市場,與大規(guī)模生產(chǎn)爬坡效應相關(guān)的主要挑戰(zhàn)正逐漸被克服。為輕松實現(xiàn)這種轉(zhuǎn)變,制造廠正在建立可與現(xiàn)存硅生產(chǎn)線共用工具的SiC生產(chǎn)線。這種安排可有效降低SiC管芯的成本,因為這樣做可與Si生產(chǎn)線分擔開銷。隨著晶圓供應商大幅度提高產(chǎn)能,近來在晶圓供貨方面的限制已不再是問題。由于4H-SiC襯底和外延生長的不斷改進,現(xiàn)在可提供晶體缺陷密度極低的高質(zhì)量6英寸晶圓。根據(jù)電氣參數(shù)測試可知,晶圓質(zhì)量越高,SiC器件的產(chǎn)量就越高。

但請務必記住,由于這些器件僅僅上市幾年,因此其現(xiàn)場可靠性數(shù)據(jù)十分有限。此外,由于SiC器件自身也面臨著一系列挑戰(zhàn),因此其認證比硅器件的認證困難得多。在SiC器件中,反向偏置條件下的電場高出將近一個數(shù)量級。如果不采用適當?shù)脑O計規(guī)則,這種高電場很容易損壞柵極氧化層。SiC柵極氧化層界面附近的陷阱密度也高得多。結(jié)果是,由于陷阱帶電,因此老化測試期間可能會出現(xiàn)不穩(wěn)定性。一直以來,我們都專注于提高長期可靠性,而取得的成果也令人欣慰,最近的報告顯示器件已通過嚴格的工業(yè)和汽車(AEC-Q101)標準認證。

除此之外,SiC供應商也已開始采取下一步行動,即為惡劣環(huán)境耐受性測試提供數(shù)據(jù)。

惡劣環(huán)境耐受性測試

作為示例,Microchip通過子公司Microsemi在其適用于700V、1200V和1700V電壓節(jié)點的SiC SBD和MOSFET上進行了惡劣環(huán)境耐受性測試。測試表明,高水平的非鉗位感應開關(guān)(UIS)耐受性對于保證器件的長期可靠性至關(guān)重要。同時還表明,在UIS測試期間,高瞬態(tài)電流流過反向偏置器件,并驅(qū)動其進入雪崩擊穿狀態(tài)。在高電流和高電壓的共同作用下,會產(chǎn)生大量熱量且溫度急劇上升。耐用功率MOSFET的局部最高溫度可達到500°C,遠高于典型溫度額定值。

UIS的耐受性與生產(chǎn)線前端和后端的外延質(zhì)量和制造工藝密切相關(guān)。即使外延中的微小晶體缺陷或與工藝相關(guān)的缺陷也可能構(gòu)成薄弱環(huán)節(jié),導致器件在UIS測試期間過早失效。這就解釋了為什么對產(chǎn)品系列耐受性的全面分析中應當包含單脈沖和重復UIS(RUIS)測試。

單脈沖測試用作篩選測試,用于識別UIS耐受性較低的器件。為了保證產(chǎn)品數(shù)據(jù)手冊中的UIS額定值,所有器件在交付給客戶之前都應經(jīng)過測試。不過,器件在現(xiàn)場投入使用期間可能會經(jīng)歷多次UIS事件。為了分析逐漸磨損的特性,需要重復測試。要深入分析特性,應對器件施加大量脈沖,常見做法是100,000次沖擊。

在UIS脈沖期間,被測器件中的電流連續(xù)降低,而電壓基本保持恒定,但會因熱效應而略微變化(圖1)。UIS脈沖的能量由脈沖開始時的最大電流和負載的電感定義。在測試過程中,通過改變電感值來調(diào)節(jié)能量。最大電流保持恒定;它等于SBD的正向電流額定值,也等于MOSFET的漏極電流額定值的三分之二。

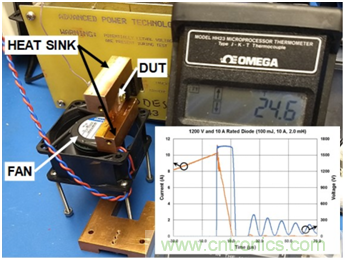

圖1:UIS脈沖期間的RUIS測試設置以及電流和電壓的波形

RUIS測試具有特定的約束條件,主要目的是防止一個脈沖與下一個脈沖的溫度發(fā)生積聚。在施加新脈沖之前,務必確保器件溫度接近環(huán)境溫度。在圖1所示的測試設置中,使用熱電偶傳感器監(jiān)視器件的溫度,并調(diào)整脈沖重復頻率以獲得恒定的讀數(shù)。為了有助于冷卻器件,應將其安裝在散熱器上風扇下方的位置。

可實現(xiàn)高雪崩耐受性的器件設計

除了采用適當?shù)臏y試過程之外,一流的UIS耐受性還需要使用下面的一組設計規(guī)則:

● 高壓端接設計有足夠高的固有擊穿電壓,以確保有效區(qū)域首先進入雪崩狀態(tài)。在這種情況下,能量會分散到整個有效區(qū)域上,而不是在狹窄的端接中,后一種情況會導致過早失效。

● MOSFET的JFET區(qū)域中的電場屏蔽對于保護柵極氧化層非常關(guān)鍵。應當謹慎優(yōu)化用于界定JFET區(qū)域的P型摻雜阱的設計和注入方案,以便提供足夠的屏蔽而不會嚴重影響導通狀態(tài)電阻。

● 利用具有高導熱率的鈍化材料為熱量通過管芯的頂部耗散提供了路徑。

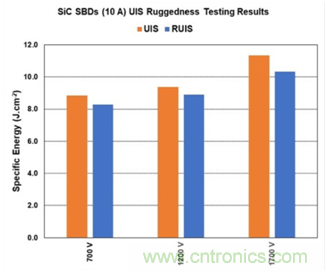

使用這些規(guī)則設計的肖特基二極管和功率MOSFET在惡劣環(huán)境耐受性測試中均表現(xiàn)良好。對SBD的測試持續(xù)到單脈沖和重復UIS失效為止,同時還監(jiān)視了多個直流參數(shù)。這項測試的結(jié)果表明,器件的正向電壓和反向泄漏電流十分穩(wěn)定,而反向擊穿電壓則略有增加,這可歸因于SiC上表面附近的自由載流子俘獲。即將失效之前的脈沖能量如圖2所示。UIS耐受性隨器件額定電壓的增大而提高。鑒于大部分熱量在外延區(qū)域產(chǎn)生,這種趨勢不難解釋。隨著外延厚度因額定電壓的增大而增加,每單位體積產(chǎn)生的熱量會減少,這反過來會降低器件中的溫度。由于重復測試的原因,UIS的耐受性會系統(tǒng)性降低,但程度很小。與單脈沖UIS相比,差異小于10%。多個UIS脈沖沒有強累加效應,預計SBD在現(xiàn)場投入使用期間將保持高耐受性。

圖2:700V、1200V和1700V SiC SBD失效前每個活動區(qū)域的比能

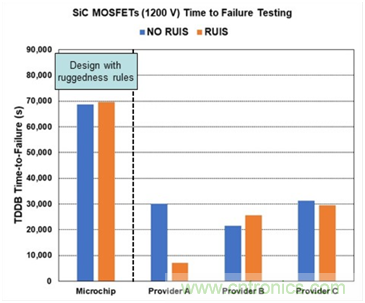

MOSFET惡劣環(huán)境耐受性特性分析應重點關(guān)注柵極氧化層的長期可靠性,這無需對器件施壓至失效。作為替代,可使用由100,000個能量相對較低的脈沖組成的重復測試。舉例來說,Microsemi 1200V/40 mΩ MOSFET使用雪崩耐受性規(guī)則進行設計,通過100 mJ脈沖進行測試,其單脈沖UIS額定值為2.0J。大多數(shù)直流參數(shù)不受影響;不過,由于該測試對柵極氧化層施壓,因此會觀察到柵極泄漏的適度增加。為了確定長期可靠性是否受到損害,我們對器件施加了隨時間變化的介電擊穿。圖3報告了對各種器件的柵極施加50 µA直流電流時的失效時間,具體包括使用公司的雪崩耐受性規(guī)則開發(fā)的Microsemi SiC器件以及其他三家領(lǐng)先供應商提供的器件。

圖3:四家供應商提供的1200V MOSFET的TDDB失效時間

堅持采用SiC

在工業(yè)和汽車市場中采用SiC器件時,需滿足嚴格的長期可靠性要求。滿足這些要求的最佳策略是使產(chǎn)品通過汽車AEC-Q101標準認證,并對尚未標準化的極端環(huán)境耐受性測試進行特性分析。通過應用設計規(guī)則來實現(xiàn)高雪崩耐受性同樣十分重要。這些措施一起使用時,不僅有助于確保SiC器件在快速普及的道路上繼續(xù)前進,同時還能提供這些應用所需的長期可靠性。

作者:

Microchip子公司Microsemi器件設計工程師Amaury Gendron-Hansen

Microchip子公司MicrosemiSiC技術(shù)開發(fā)總監(jiān)Avinash Kashyap

Microchip子公司Microsemi器件/開發(fā)工程總監(jiān)Dumitru Sdrulla

推薦閱讀: