【導(dǎo)讀】在考慮配電網(wǎng)(PDN)阻抗與同時(shí)開關(guān)噪聲(SSN)和電磁兼容性(EMC)的關(guān)系時(shí),了解去耦合的影響至關(guān)重要。如果一個(gè)PCB的功率完整性或去耦合特性較差,例如高PDN阻抗, 就會(huì)產(chǎn)生SSN和EMC問題。本文將通過實(shí)際案例,來證實(shí)PCB的PDN阻抗、SSN和EMC之間的關(guān)系。

本文通過實(shí)際案例,來證實(shí)PCB的PDN阻抗、SSN和EMC之間的關(guān)系。

在考慮配電網(wǎng)(PDN)阻抗與同時(shí)開關(guān)噪聲(SSN)和電磁兼容性(EMC)的關(guān)系時(shí),了解去耦合的影響至關(guān)重要。如果一個(gè)PCB的功率完整性或去耦合特性較差,例如高PDN阻抗, 就會(huì)產(chǎn)生SSN和EMC問題。本文將通過實(shí)際案例,來證實(shí)PCB的PDN阻抗、SSN和EMC之間的關(guān)系。

分析和結(jié)果

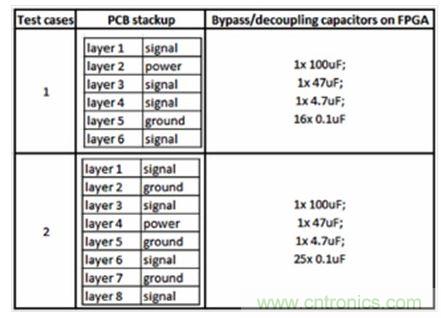

測試的原型為下面兩個(gè)版本:一個(gè)由晶體振蕩器提供外部50MHz參考的FPGA;三個(gè)主要接口:350MHz時(shí)鐘速率的DDR2 SDRAM、150MHz的ADC數(shù)據(jù)總線和100MHz 的以太網(wǎng)。所有這些元器件都由1.8V降壓轉(zhuǎn)換器供電。通過表1中列出的測試案例,可以了解去耦合(包括PCB疊層和電容器)對SSN和EMC的影響。

在測試案例1中,原型PCB包括四個(gè)信號層和一個(gè)接地層,有16個(gè)0.1μF去耦合電容器連接到PCB上FPGA的+1.8V電源引腳。在測試案例2中,原型PCB包括四個(gè)信號層和三個(gè)接地層,有25個(gè)0.1μF去耦合電容器連接到PCB 上FPGA的+1.8V電源引腳。

表1. 研究PCB去耦合對SSN和EMC影響的測試案例。

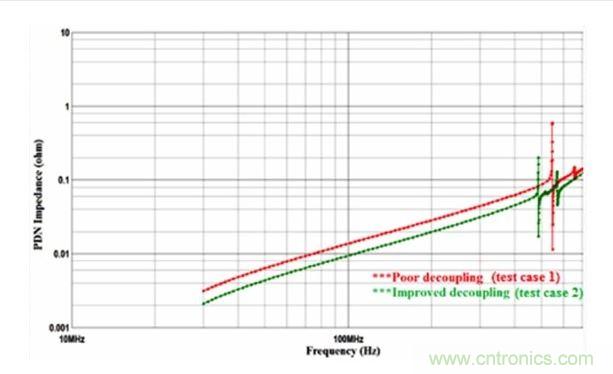

由圖1的PDN阻抗曲線可以看出( 使用Mentor Graphic Hyperlynx軟件對布局后期的功率完整性進(jìn)行分析),相比測試案例1,測試案例2的電力網(wǎng)有更好的去耦合條件,因而在寬帶范圍內(nèi)有更低的阻抗。0.1μF的電容器在中低頻段(< 400MHz)會(huì)產(chǎn)生影響。另外,接地層的平面電容在頻率高于400MHz時(shí)會(huì)產(chǎn)生影響。與測試案例1相比, 測試案例2有更多的去耦合電容器和接地層,因而具有更低的PDN阻抗。

圖 1. PDN 阻抗圖

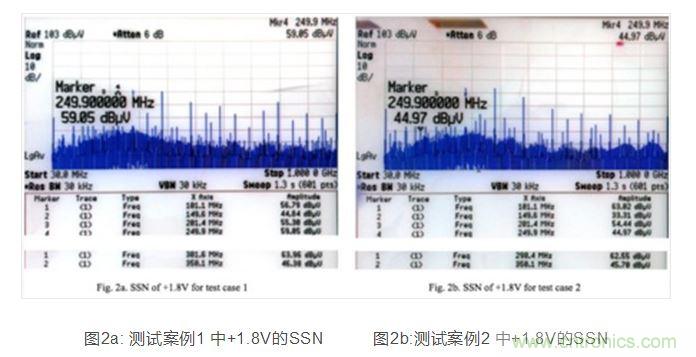

然后,對兩個(gè)測試案例中頻率跨越30MHz至1000MHz時(shí)+1.8V(使用頻譜分析儀通過交流耦合探測)的功率頻譜進(jìn)行比較。參見圖2b所示的測試案例2的頻譜,所觀察到的雜散主要是由晶體振蕩器(50MHz基頻)、DDR2 SDRAM (350MHz基頻)、ADC數(shù)據(jù)總線(150MHz基頻)和以太網(wǎng)(100MHz基頻)的諧波造成的。在圖2a所示的測試案例1中, 由于去耦合性能較差,頻譜上出現(xiàn)了雜散,其功率達(dá)到最高。

PDN阻抗和晶體振蕩器瞬態(tài)電流之間的相互作用, 加上在特定頻率上同時(shí)開關(guān)或切換的IC輸出緩沖器(即SSN),共同產(chǎn)生了電網(wǎng)噪聲。通過改善去耦合降低功率阻抗,SSN和頻率雜散便能得到抑制。

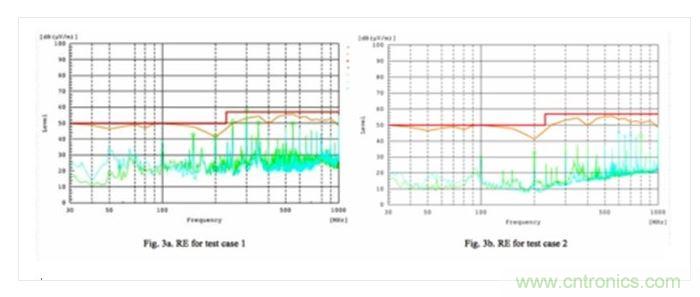

通過在3米的電波暗室進(jìn)行輻射發(fā)射(RE)測試可以比較 兩種測試案例的原型之間的噪聲性能。測試案例2顯示出比測試案例1更好的RE或EMC性能,測試案例2中有更多的接地層,這不僅能改善去耦合或PDN阻抗,還為沿PCB 跡線傳輸?shù)乃行盘柼峁┝饲‘?dāng)?shù)姆祷芈窂?,從而進(jìn)一步降低了輻射發(fā)射。

圖3a: 測試案例1的RE 圖3b:測試案例2的RE

結(jié)論

實(shí)際測試證實(shí)了去耦合對SSN和EMC的確會(huì)產(chǎn)生影響。因此,PDN和PCB疊層必須采用嚴(yán)格的方式執(zhí)行, 以確保原型具有出色的質(zhì)量、穩(wěn)健性和功能。