【導(dǎo)讀】設(shè)計(jì)人員可以通過控制器的開關(guān)頻率抖動(dòng)�����,減少一個(gè)脈沖寬度調(diào)制(PWM)控制器的電磁干擾(EMI)分布中頻譜分量的峰值幅度�����。時(shí)鐘抖動(dòng)擴(kuò)頻技術(shù)并非意在取代傳統(tǒng)的EMI降低技術(shù)�,但它們與傳統(tǒng)技術(shù)的結(jié)合使用,可以減少系統(tǒng)中的EMI分布�����。它們還可以利用減少通過某些排放標(biāo)準(zhǔn)所需的屏蔽和濾波量來降低成本�。

我們采用外部擴(kuò)頻抖動(dòng)時(shí)鐘源,既有IC也有FPGA�����,來驅(qū)動(dòng)PWM降壓轉(zhuǎn)換器����,結(jié)果如下所述����。 如果FPGA時(shí)鐘源已存在于系統(tǒng)中,由于不需要添加額外的組件�,因此它將是一個(gè)更好的選擇��。

專用IC擴(kuò)頻抖動(dòng)的時(shí)鐘源為Exar g公司的PowerXR設(shè)備提供時(shí)鐘脈沖�����。PowerXR讓設(shè)計(jì)師可以靈活地選擇一個(gè)PWM控制器開關(guān)頻率���,以及自如地實(shí)現(xiàn)外部時(shí)鐘源的同步。

原理

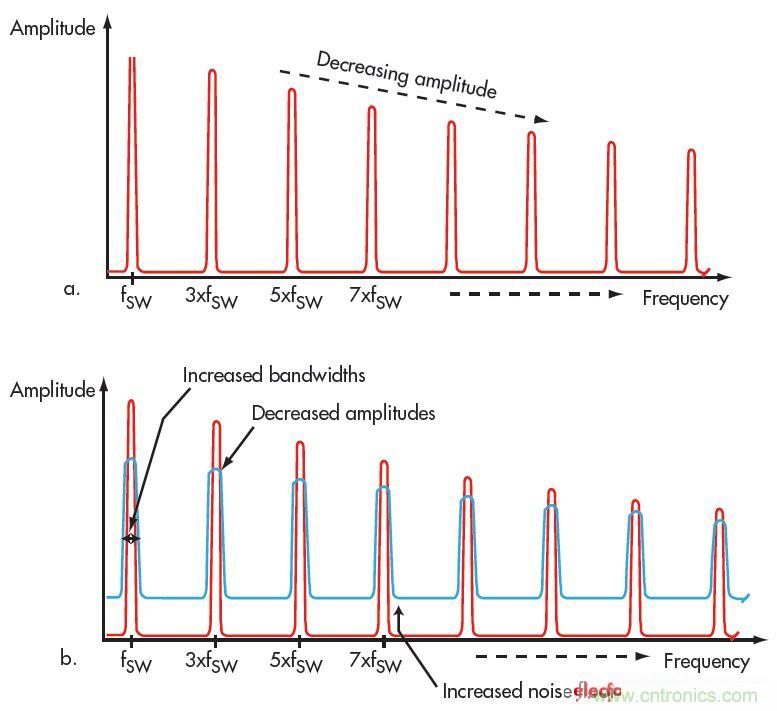

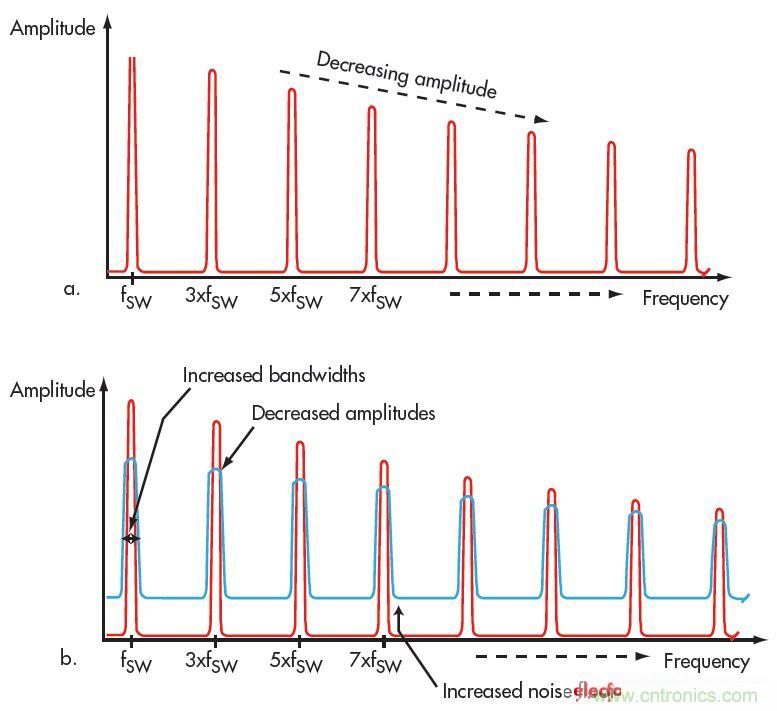

在常見的PWM控制器中�,時(shí)鐘波形是一個(gè)方波,其頻譜由基本開關(guān)頻率�����、fsw和高階奇次諧波組成(圖1a)���。 通過三角波調(diào)制基頻進(jìn)行擴(kuò)頻�����,可以在更寬的頻帶上分散基頻和高次諧波中集中的能量�,從而減少峰值排放(圖1b)�����。 由于寬頻能量保持恒定,擴(kuò)頻還能增加噪底����。

圖1: (a) 非抖動(dòng)時(shí)鐘的頻譜。 (b) 抖動(dòng)時(shí)鐘頻譜(藍(lán)色)����。

例如,如果fsw = 300千赫��,所得到的高次諧波將是900千赫����、1.5兆赫、2.1兆赫等�����。隨著高次諧波振幅的減少�,基本開關(guān)頻率的振幅將是最高的。

實(shí)際輻射分量的振幅將取決于輻射傳輸效率以及其它諸多因素的影響�,包括頻率、布局和路徑長度��。 但振幅一般會(huì)隨著頻率的增加而減少���,其中有一個(gè)或多個(gè)頻率的輻射可能比其他的更有效�����。

在兩個(gè)邊界頻率之間調(diào)制基本開關(guān)頻率稱為時(shí)鐘抖動(dòng)��。 PWM控制器基本開關(guān)頻率的抖動(dòng)會(huì)在一個(gè)相當(dāng)窄的頻帶內(nèi)改變基本開關(guān)頻率��。 例如����,如果fsw = 300千赫��,則此頻率的±1.5%對(duì)稱抖動(dòng)(簡稱為中心抖動(dòng))加上三角波的抖動(dòng)作用�����,將產(chǎn)生從295.5千赫至304.5千赫的PWM控制器開關(guān)頻率范圍�����。

所得到的抖動(dòng)頻譜顯示了各種頻譜分量振幅的減少及其各自頻寬的增加�。 同時(shí),由于寬頻能量保持恒定,還出現(xiàn)了噪底的增加�����。

抖動(dòng)頻率fDITHER通常介于20和40千赫之間��。 雖然更復(fù)雜的調(diào)制波形不無可能�,但事實(shí)證明簡單的三角形波形產(chǎn)生效果最好。 同時(shí)����,經(jīng)證明,時(shí)鐘抖動(dòng)導(dǎo)致了頻譜分量振幅減少��,這可以通過以下公式來說明:

頻譜衰減[dB]=10*log[(fsw*d)/(fDITHER/n)]

其中:

fsw = PWM控制器開關(guān)頻率(介于PowerXR設(shè)備的300 kHz和1.5 MHz之間)

d = 基本開關(guān)頻率的抖動(dòng)百分比(通常介于±0.25%和±5%之間)

fDITHER = 抖動(dòng)調(diào)制率(通常介于20 kHz和60 kHz之間)

n = 系統(tǒng)時(shí)鐘分頻器

增加d和減少fDITHER的效果一樣���。

專用擴(kuò)頻時(shí)鐘發(fā)生器

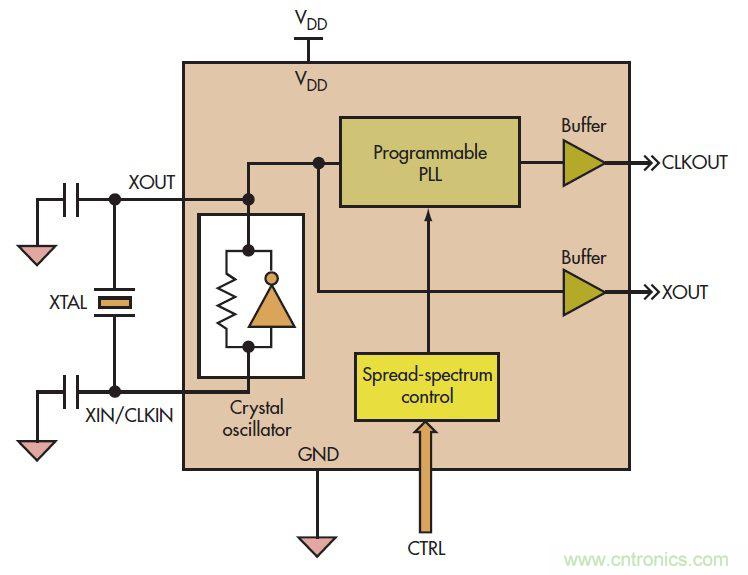

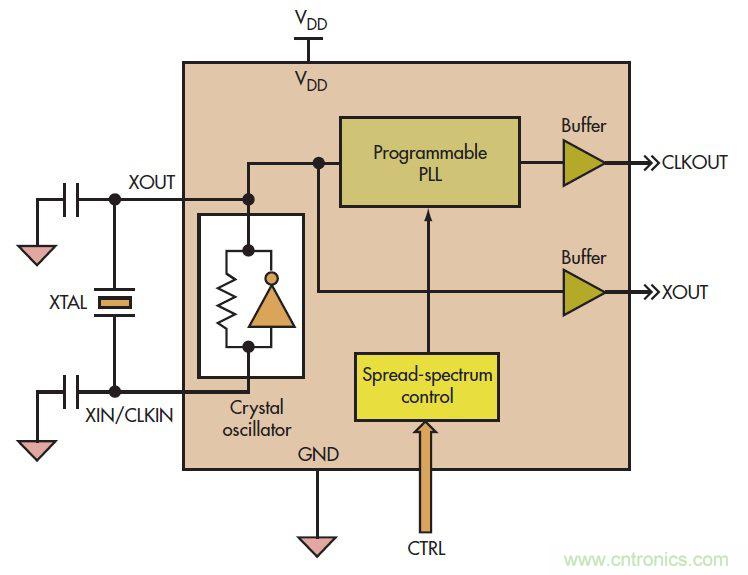

一些廠家生產(chǎn)專用的IC時(shí)鐘抖動(dòng)擴(kuò)頻時(shí)鐘發(fā)生器����。 在常見設(shè)備中�����,IC的參考時(shí)鐘源來自外部晶振(XTAL)或外部時(shí)鐘源(CLKIN)(圖2)����。

圖2: 專用IC擴(kuò)頻時(shí)鐘發(fā)生器框圖�����。

根據(jù)晶振或外部時(shí)鐘源頻率,可編程的相位鎖定回路(PLL)可產(chǎn)生范圍從幾MHz到超過100 MHz時(shí)鐘源���。

許多外部擴(kuò)頻控制線通?����?捎糜诳刂葡鄬?duì)于參考時(shí)鐘源頻率的抖動(dòng)范圍����。 這些控制線也可決定時(shí)鐘頻譜將是中心抖動(dòng)�、向下抖動(dòng),或相對(duì)于參考時(shí)鐘源頻率的向上抖動(dòng)����。

所支持的參考頻率的確切范圍將取決于IC,但它通常涵蓋的范圍很廣�,足以支持驅(qū)動(dòng)器所需的系統(tǒng)時(shí)鐘頻率。因?yàn)榫д裰圃焐毯芏?����,因所以找到一個(gè)比較接近所需系統(tǒng)時(shí)鐘頻率的產(chǎn)品輕而易舉。

例如��,如果所需的PowerXR系統(tǒng)時(shí)鐘頻率為28.8 MHz(300 kHz PWM開關(guān)頻率)����,則合適的晶振可能是Abracon ABLS-28.63636MHZ-B4-FT,可以產(chǎn)生28.63636 MHz的頻率�����,�����, 符合PowerXR系統(tǒng)時(shí)鐘頻率0.57%的范圍 這可可以允許參考時(shí)鐘源頻率±1.1%左右的中心抖動(dòng)�����,同時(shí)保持在PowerXR設(shè)備要求的所需±5%同步范圍內(nèi)����。

使用抖動(dòng)FPGA設(shè)備

有關(guān)實(shí)施擴(kuò)頻時(shí)鐘發(fā)生器的詳細(xì)信息可從FPGA廠商處獲得。 如果系統(tǒng)現(xiàn)有用的FPGA資源�,與前面討論的專用IC方法相比����,在FPGA中實(shí)施擴(kuò)頻時(shí)鐘發(fā)生器可以節(jié)省成本和空間����。

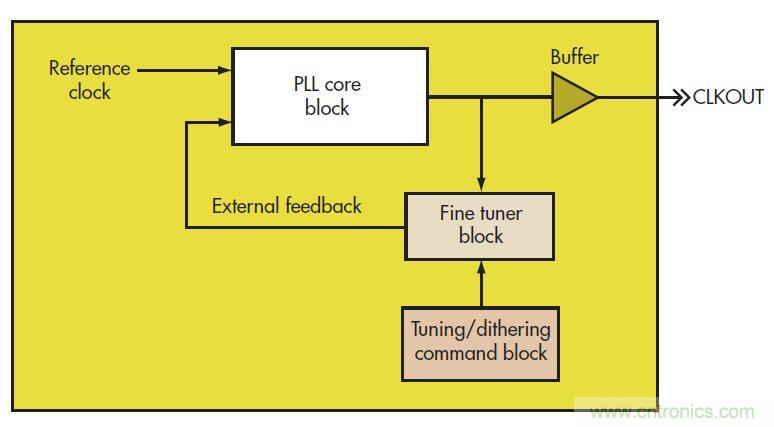

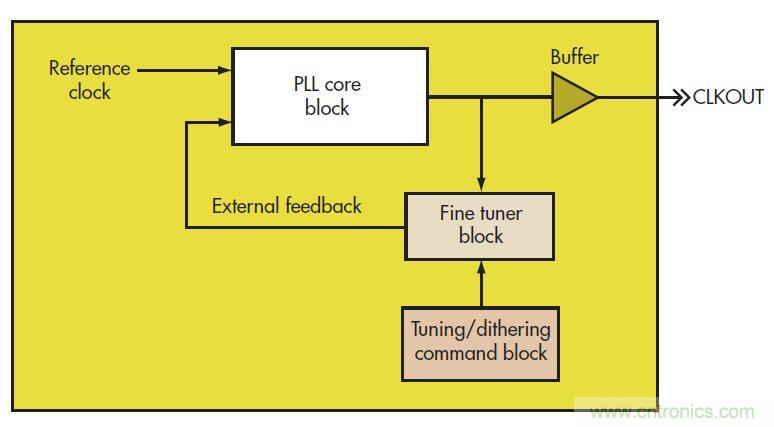

以用FPGA實(shí)施的常用擴(kuò)頻時(shí)鐘發(fā)生器框圖為例(圖3)。 大多數(shù)FPGA廠商提供擴(kuò)頻模塊或基原���,可以用來從參考時(shí)鐘源產(chǎn)生時(shí)鐘抖動(dòng)信號(hào)。

圖3: FPGA擴(kuò)頻時(shí)鐘發(fā)生器框圖���。

參考時(shí)鐘通常來自分頻器或倍頻模塊����,并且頻率與所需的系統(tǒng)時(shí)鐘頻率相同���。 微調(diào)模塊由調(diào)諧/抖動(dòng)命令模塊控制��,并使用可配置的頻率階躍和其間可配置的時(shí)間間隔���,向上和向下調(diào)節(jié)PLL輸出頻率(CLKOUT)。 PLL內(nèi)核模塊配置詳情可以從FPGA廠商處獲得�����,但如圖所示,內(nèi)部反饋回路通常為斷開狀態(tài)��,微調(diào)模塊則被放置在外部反饋環(huán)路中�����。

連接驅(qū)動(dòng)器

PowerXR設(shè)備使用一個(gè)可編程的系統(tǒng)時(shí)鐘頻率和一個(gè)可編程的分頻器來產(chǎn)生PWM控制器的開關(guān)頻率��,fsw���。如果對(duì)這些設(shè)備進(jìn)行配置���,從外部同步時(shí)鐘源操作,時(shí)鐘源的頻率必須在內(nèi)部系統(tǒng)時(shí)鐘頻率的±5%范圍之內(nèi)����。

數(shù)據(jù)表中提供了一個(gè)表格,有助于確定下分頻的系數(shù)n�。例如,對(duì)于在300 kHz的操作���,系統(tǒng)時(shí)鐘頻率可能是28.8 MHz���, n值為96�����。在此情況下����,d的頻譜衰減 = ±1.1%(即2.2%)���,fDITHER = 56 kHz為:

頻譜衰減 = 10*log[(fsw*d)/(fDITHER/n)] = 10*log[(300 kHz)*(0.022)/(56 kHz/96) = 10.5 dB。

因此�����,除了所有諧波外����,基頻的振幅將衰減約10.5 dB。

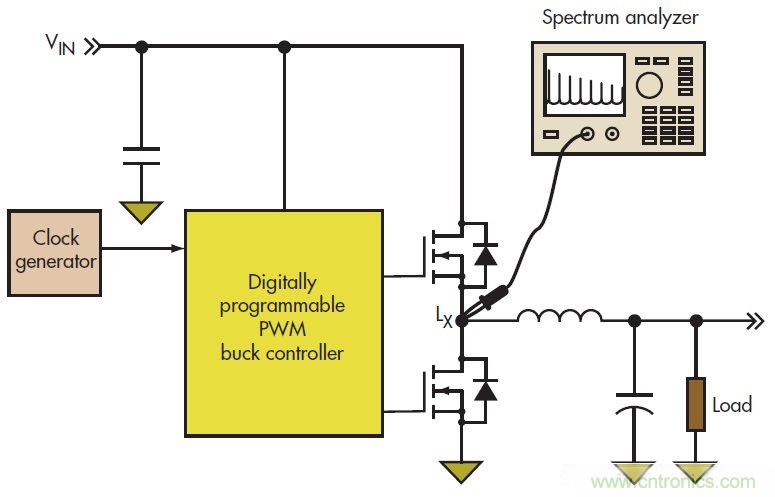

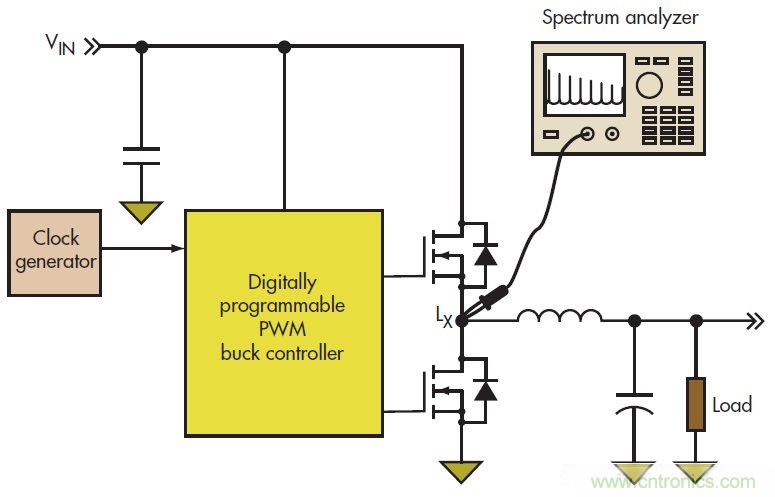

測(cè)試配置

在用于收集非抖動(dòng)和抖動(dòng)時(shí)鐘源的排放數(shù)據(jù)的測(cè)試設(shè)置中����,PowerXR設(shè)備同步至?xí)r鐘發(fā)生器提供的外部時(shí)鐘源(圖4)。 電路中的LX節(jié)點(diǎn)是用于收集非抖動(dòng)和抖動(dòng)排放數(shù)據(jù)的測(cè)量點(diǎn)�,因?yàn)樗俗罡叩碾妷悍逯岛退邢嚓P(guān)的輻射頻譜分量����。

圖4: 測(cè)試設(shè)置��。

雖然在LX節(jié)點(diǎn)收集的數(shù)據(jù)不是實(shí)際的輻射排放數(shù)據(jù)����,因?yàn)樗话總€(gè)頻譜分量的輻射效率,但可將它用于比較非抖動(dòng)和抖動(dòng)時(shí)鐘數(shù)據(jù)之間的相對(duì)水平�。

XRP7714 PowerXR設(shè)備是一個(gè)4通道數(shù)字PWM降壓控制器,但僅啟用通道1并用于收集排放數(shù)據(jù)���。 外部同步時(shí)鐘源連接到其中一個(gè)通用I/O (GPIO)端口���。

PowerXR設(shè)備使用PowerArchitect開發(fā)軟件在I2C端口上配置。該軟件可從Exar網(wǎng)站下載�����。 如先前所討論的�,該設(shè)備針對(duì)基于28.8 MHz系統(tǒng)時(shí)鐘頻率的300 kHz PWM開關(guān)頻率進(jìn)行配置。

測(cè)量的數(shù)據(jù)

基線排放數(shù)據(jù)的收集采用了零擴(kuò)展��、外加上述±1.1%中心擴(kuò)展的28-MHz ModOUT時(shí)鐘源收����。 28.63636-MHz ±1.1%抖動(dòng)時(shí)鐘源的抖動(dòng)頻率范圍是:

fmax = (28.63636 MHz)(1.011)/n = (28.63636 MHz)(1.011)/96 = 301.6 kHz

fnom = 28.63636 MHz/n = 28.63636 MHz/96 = 298.3 kHz

fmin = (28.63636 MHz)(1 – 0.011)/n = (28.63636 MHz)(1 – 0.011)/96 = 295.0 kHz

該數(shù)據(jù)表示+1.07%/–1.01% (2.08%)的頻率擴(kuò)展�����,這與±1.1%(2.2%)的預(yù)期擴(kuò)展非常接近����。 與預(yù)期的一樣���,基準(zhǔn)頻率在fnom = 295.3 kHz時(shí)進(jìn)行測(cè)量��。 每個(gè)波形的占空比是50%左右�����,和VOUT1/VIN = 5 V/10 V = 0.5電壓轉(zhuǎn)換比所預(yù)示的一樣。

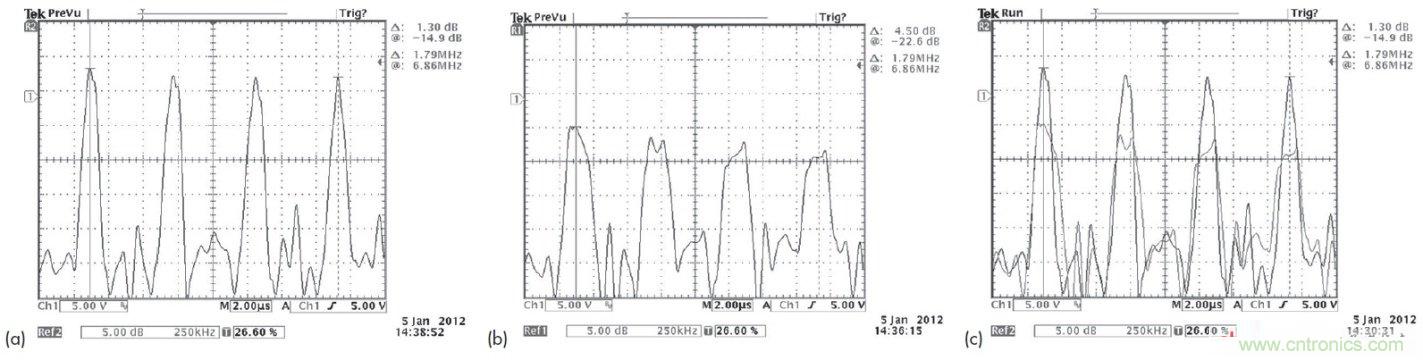

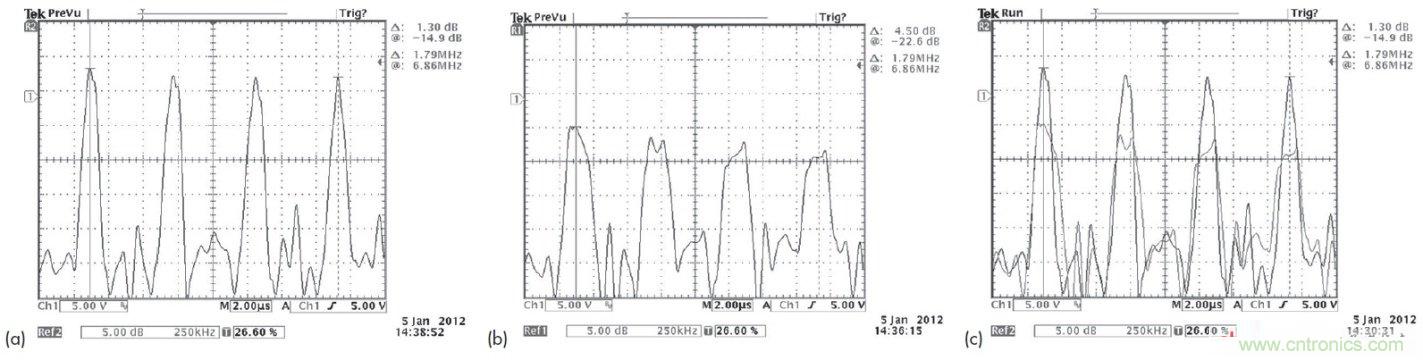

非抖動(dòng)和抖動(dòng)頻譜的頻域圖像表明所有抖動(dòng)頻譜分量振幅低于相應(yīng)的非抖動(dòng)組件���,而且它們的寬度也稍大��。 這在疊加波形時(shí)更明顯(圖5)���。 頻率介于6.50和9.00 MHz之間���。 示波器的噪底性能的限制,妨礙了在更高頻率下的精確測(cè)量����,但這些情況可作為在更高頻率下預(yù)期行為的很好的例證。

圖5: (a) 非抖動(dòng)頻譜���。 (b) 抖動(dòng)頻譜��。 (c) 兩個(gè)頻譜的重疊��。

示波器中內(nèi)置的快速傅立葉變換(FFT)功能有局限性�����,因此導(dǎo)致頻譜分量的振幅�、寬度和整體形狀有些失真���,但它仍然可用于說明頻率抖動(dòng)技術(shù)的優(yōu)點(diǎn)���。

較大主頻譜分量之間的低振幅頻譜分量是由于占空比恰好不是50%。 當(dāng)一個(gè)時(shí)域的脈沖串有一個(gè)恰好為50%的占空比,所得到的高次頻譜分量是基頻的奇數(shù)倍�,而對(duì)于非50%的占空比,所得到的頻譜分量是基頻的整數(shù)倍����。

推薦閱讀: