【導(dǎo)讀】電力電子世界在1959年取得突破,當(dāng)時Dawon Kahng和MarTIn Atalla在貝爾實驗室發(fā)明了金屬氧化物半導(dǎo)體場效應(yīng)晶體管(MOSFET)。首款商業(yè)MOSFET在五年后發(fā)布生產(chǎn),從那時起,幾代MOSFET晶體管使電源設(shè)計人員實現(xiàn)了雙極性早期產(chǎn)品不可能實現(xiàn)的性能和密度級別。

然而,近年來,這些已取得的進步開始逐漸弱化,為下一個突破性技術(shù)創(chuàng)造了空間和需求。這就是氮化鎵(GaN)引人注目的地方。

作為一種寬帶隙晶體管技術(shù),GaN正在創(chuàng)造一個令人興奮的機會,以實現(xiàn)電力電子系統(tǒng)達到新的性能和效率。GaN的固有優(yōu)勢為工程師開啟了重新考慮功率密度的方法,這些方法在以前并不可能實現(xiàn),如今能滿足世界日益增長的電力需求。在這篇文章中,我將探討如何實現(xiàn)。

為何選擇GaN?

當(dāng)涉及功率密度時,GaN為硅MOSFET提供了幾個主要優(yōu)點和優(yōu)勢,包括:

• 較低的RDS(on):如表1所示,GaN的MOSFET面積為RDS(on)的一半。這直接使電路中傳導(dǎo)損耗降低了50%。因此,您可以在設(shè)計中使用較小的散熱器和更簡單的熱管理。

• 較低的柵極和輸出電荷:GaN提供較低的柵極電荷。與MOSFET的4nC相比,典型的中壓器件具有大約1nC的柵極電荷(表2)。較低的柵極電荷使設(shè)計具有更快的導(dǎo)通時間和轉(zhuǎn)換速率,同時減少損耗。

類似地,GaN具有顯著較低的輸出電荷(表2),這為每個設(shè)計帶來雙重優(yōu)勢。首先,開關(guān)損耗下降多達80%,結(jié)合較低的傳導(dǎo)損耗,對功率密度有重大和積極的影響。第二,根據(jù)拓撲和應(yīng)用,設(shè)計可在更高的開關(guān)頻率運行高達10倍。這大大減少了磁性材料的尺寸以及設(shè)計的尺寸和占用空間,同時將整體效率提高了15%。

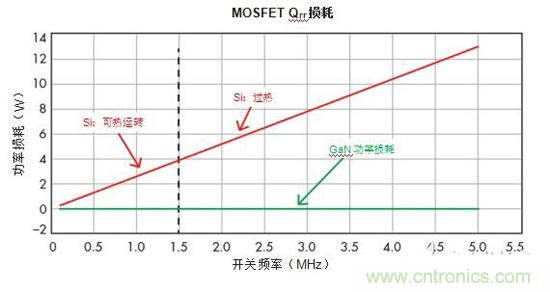

• 零反向恢復(fù):硅MOSFET在50至60 nC范圍內(nèi)具有典型的反向恢復(fù)電荷,具體取決于其尺寸和特性。當(dāng)MOSFET關(guān)斷時,體二極管中的反向恢復(fù)電荷(Qrr)產(chǎn)生損失,從而增加了總的系統(tǒng)開關(guān)損耗。這些損耗與開關(guān)頻率成正比。如圖1所示,較高頻率下的Qrr損耗使得MOSFET在許多應(yīng)用中變得不切實際。

1.相比GaN替代品,MOSFET的反向恢復(fù)電荷(Qrr)損耗在較高頻率下要大得多。

相比之下,GaN具有零反向恢復(fù)和零Qrr損耗,使GaN FET成為硬切換應(yīng)用的理想選擇,如稍后的示例所示。

驅(qū)動GaN

不管所用的GaN類型如何,柵極驅(qū)動設(shè)計對于實現(xiàn)最佳的整體性能至關(guān)重要。一個糟糕的柵極驅(qū)動設(shè)計的一個很好的類比是在一級方程式賽車上使用街胎。

在設(shè)計柵級驅(qū)動器時,請注意以下幾個關(guān)鍵參數(shù):

• 偏置電壓:重要的是將柵極偏置為最佳電壓以獲得最佳的開關(guān)性能,同時保護柵極免受潛在的過壓狀況。偏置電平隨類型和GaN制造工藝而異,需要相應(yīng)設(shè)置。具有鉗位或過壓保護電路也極其關(guān)鍵。

• 環(huán)路電感:由于GaN的高壓擺率和開關(guān)頻率,設(shè)計中的任何寄生電感都會在系統(tǒng)中引入損耗和振鈴。許多電感源存在于GaN FET和驅(qū)動器封裝中的引線和內(nèi)部接合線以及印刷電路板(PCB)跡線的設(shè)計中。雖然可將其減少,但很難消除它們。諸如LMG3410的GaN功率級解決方案將驅(qū)動器和GaN FET集成到單個封裝中,顯著降低了總體電感。

• 傳播延遲:短傳播延遲和良好匹配(針對半橋拓撲)對于高頻操作非常重要。25 ns的傳播延遲和1到2 ns的匹配是高頻(1 MHz或更高)設(shè)計的一個很好的起點。

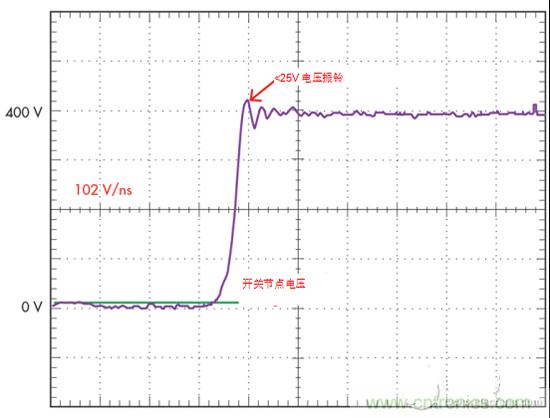

2.如通過優(yōu)化的驅(qū)動器設(shè)計的GaN開關(guān)波形所證明的,GaN可以非常高速的轉(zhuǎn)換速率工作,并且使交換節(jié)點上的振鈴最小。

通過最佳的柵極驅(qū)動設(shè)計和PCB布局,您可以非常高的轉(zhuǎn)換速率(》 100 V / ns)運行GaN,使交換節(jié)點上的振鈴最小。圖2所示為這種設(shè)計的開關(guān)波形的示例。

設(shè)計實例:下一代PFC解決方案

由于其獨特的特性,GaN幫助電源設(shè)計人員克服了不同系統(tǒng)和應(yīng)用中功率密度方面最困難的挑戰(zhàn)。這些好處不是來自于在現(xiàn)有設(shè)計中簡單地將MOSFET替換為等效GaN。GaN使得以前不可能使用硅MOSFET實現(xiàn)的新電路拓撲結(jié)構(gòu)和/或工作模式變?yōu)楝F(xiàn)實。顯著的優(yōu)勢導(dǎo)致新一代的產(chǎn)品尺寸更小、效率更高。我們來看一個這樣的示例。

功耗因數(shù)校正(PFC)在消耗大于75W的每個電氣或電子產(chǎn)品中是強制性的。PFC是位于電源和系統(tǒng)其余部分之間的第一個電源轉(zhuǎn)換模塊,并在任何給定的工作點承載整個負載。因此,它直接影響整個系統(tǒng)的大小和效率。

已設(shè)計出不同拓撲的一代產(chǎn)品,旨在減小尺寸,同時滿足行業(yè)標(biāo)準的效率。例如,在80 Plus中定義的效率水平對于鈦級電源需要96%的效率。

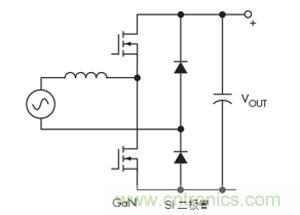

3.雙橋PFC拓撲通常用于許多大功率設(shè)計。

許多大功率系統(tǒng)(> 1 kW)采用雙橋拓撲結(jié)構(gòu)(圖3)。隨著碳化硅(SiC)二極管和最新一代的超結(jié)MOSFET晶體管的引入,我們已經(jīng)看到過去十年中功率密度方面的改進。然而,這些改進已達到效率和功率密度的停滯期。

功率密度的顯著增加需要一種替代方法:

• 電源開關(guān)的數(shù)量

• 濾波電感的數(shù)量

• 電感器的尺寸

• 散熱片和冷卻元件的尺寸

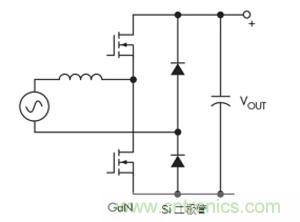

一種替代方案是連續(xù)導(dǎo)通模式圖騰柱拓撲。這種拓撲結(jié)構(gòu)充分利用了GaN的所有關(guān)鍵特性,最終導(dǎo)致尺寸更小、工作頻率更高的設(shè)計(圖4)。GaN的零反向恢復(fù)對于實現(xiàn)該拓撲特別重要。

4.圖騰柱PFC拓撲結(jié)構(gòu)在降低工作頻率的同時降低設(shè)計尺寸,充分利用了GaN的零反向恢復(fù)。

表3總結(jié)了這種無橋PFC設(shè)計的幾個主要優(yōu)點,并做了進一步闡述:

• 電源開關(guān):與雙橋拓撲相比,圖騰柱PFC替代了兩個超結(jié)MOSFET和兩個僅具有兩個GaN器件的SiC二極管。

• 濾波電感器:該拓撲結(jié)構(gòu)消除了功率級中的一個龐大的濾波電感。電感器的去除及功率開關(guān)數(shù)量的減少也提高了整體系統(tǒng)的可靠性。

• 尺寸:由于GaN在高得多的開關(guān)頻率(通常為40至60 kHz條件下的MOSFET的四倍)條件下工作,您可使用較小的濾波電感。此外,GaN的較低開關(guān)損耗使得設(shè)計人員能夠在功率級中顯著縮小散熱片的尺寸。

• 效率:精心設(shè)計的圖騰柱PFC的高效率達99%以上。為了說明這一點,在整個PFC階段,1 kW的功耗消耗不到10W。

• 成本:由于其現(xiàn)有制造成本,GaN器件的溢價將更高。然而,鑒于此處節(jié)省的成本,系統(tǒng)總成本應(yīng)與現(xiàn)有的MOSFET設(shè)計相當(dāng)。

現(xiàn)代圖騰柱設(shè)計還利用數(shù)字功率控制器進一步提高效率,總諧波失真和其他關(guān)鍵設(shè)計參數(shù)。數(shù)字控制器(如C2000和UCD3138)可以智能地控制功率級操作,實時優(yōu)化效率,并響應(yīng)線路和負載條件。

結(jié)論

我們見證了需要更高功率的諸如云計算、5G電信基礎(chǔ)設(shè)施、風(fēng)電和太陽能電站及電動和混合動力汽車等行業(yè)的日益增長的需求。隨著硅MOSFET達到停滯期,設(shè)計人員正在探索寬帶隙技術(shù),如GaN的下一個設(shè)計。

如PFC示例所示,GaN不僅提高了效率,而且將電源的尺寸大大降低了30%至50%。你可以在隔離或非隔離的dc-dc轉(zhuǎn)換器、逆變器和其它電源轉(zhuǎn)換子系統(tǒng)中使用GaN,以顯著降低功耗、部件數(shù)量、重量和尺寸。