【導(dǎo)讀】短時(shí)毛刺脈沖干擾是一個(gè)非常重要的動(dòng)態(tài)非線性的DAC特性,你將會(huì)在器件以工作采樣率運(yùn)行時(shí)遇到這個(gè)問題。但是,這只是冰山一角。影響高速電路的其它因素還有轉(zhuǎn)換率和穩(wěn)定時(shí)間。請(qǐng)隨時(shí)關(guān)注下一篇與這一主題相關(guān)的文章。

在DAC基礎(chǔ)知識(shí):靜態(tài)技術(shù)規(guī)格中,我們探討了靜態(tài)技術(shù)規(guī)格以及它們對(duì)DC的偏移、增益和線性等特性的影響。這些特性在平衡雙電阻 (R-2R) 和電阻串?dāng)?shù)模轉(zhuǎn)換器 (DAC) 的各種拓?fù)浣Y(jié)構(gòu)間是基本一致的。然而,R-2R和電阻串DAC的短時(shí)毛刺脈沖干擾方面的表現(xiàn)卻有著顯著的不同。

我們可以在DAC以工作采樣率運(yùn)行時(shí)觀察到其動(dòng)態(tài)不是線性。造成動(dòng)態(tài)非線性的原因很多,但是影響最大的是短時(shí)毛刺脈沖干擾、轉(zhuǎn)換率/穩(wěn)定時(shí)間和采樣抖動(dòng)。

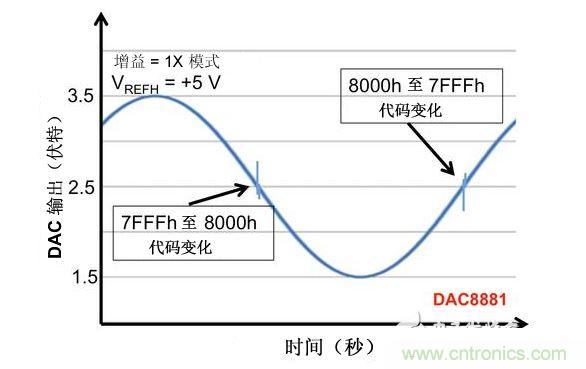

用戶可以在DAC以穩(wěn)定采樣率在其輸出范圍內(nèi)運(yùn)行時(shí)觀察短時(shí)毛刺脈沖干擾。圖1顯示的是一個(gè)16位R-2R DAC,DAC8881上的此類現(xiàn)象。

圖1

這個(gè)16位DAC (R-2R) 輸出顯示了7FFFh – 8000h代碼變化時(shí)的短時(shí)毛刺脈沖干擾的特性。

到底發(fā)生了什么?

在理想情況下,DAC的輸出按照預(yù)期的方向從一個(gè)電壓值移動(dòng)到下一個(gè)電壓值。但實(shí)際情況中,DAC電路在某些代碼到代碼轉(zhuǎn)換的過程中具有下沖或過沖特性。

這一特性在每一次代碼到代碼轉(zhuǎn)換時(shí)都不一致。某些轉(zhuǎn)換中產(chǎn)生的下沖或過沖特性會(huì)比其它轉(zhuǎn)換更加明顯。而短時(shí)毛刺脈沖干擾技術(shù)規(guī)格量化的就是這些特性。DAC短時(shí)毛刺脈沖干擾會(huì)瞬時(shí)輸出錯(cuò)誤電壓來干擾閉環(huán)系統(tǒng)。

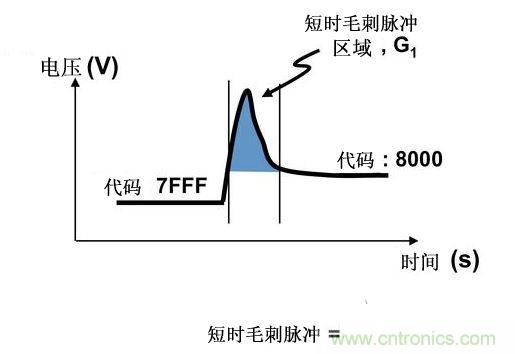

圖2顯示的是具有單突短時(shí)毛刺脈沖干擾的DAC的示例。一個(gè)電阻串DAC產(chǎn)生的通常就是這種類型的短時(shí)毛刺脈沖干擾。

圖2

單突DAC輸出短時(shí)毛刺脈沖干擾特性。

在圖2中,代碼轉(zhuǎn)換的位置是從7FFFh到8000h。如果你將這些數(shù)變換為二進(jìn)制形式,需要注意的是這兩個(gè)十六進(jìn)制代碼的每個(gè)位或者從1變換為0,或者從0變換為1。

短時(shí)毛刺脈沖干擾技術(shù)規(guī)格量化了這個(gè)毛刺脈沖現(xiàn)象所具有的能量,能量單位為納伏秒,即nV-sec (GI)。這個(gè)短時(shí)毛刺脈沖干擾的數(shù)量等于曲線下面積的大小。

單突短時(shí)毛刺脈沖干擾是由DAC內(nèi)部開關(guān)的不同步造成的。那是什么引起了這一DAC現(xiàn)象呢?原因就是內(nèi)部DAC開關(guān)的同步不總是那么精確。由于集成開關(guān)電容充電或放電,你能在DAC的輸出上看到這些電荷交換。

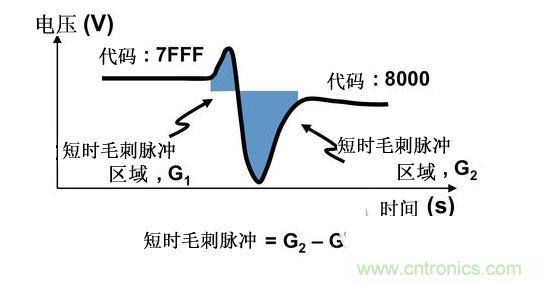

R-2R DAC產(chǎn)生兩個(gè)區(qū)域的短時(shí)毛刺脈沖干擾錯(cuò)誤(圖3)。由于出現(xiàn)了雙脈沖誤差,從負(fù)短時(shí)毛刺脈沖干擾 (G1) 中減去正短時(shí)毛刺脈沖干擾 (G2) 來產(chǎn)生最終的短時(shí)毛刺脈沖干擾技術(shù)規(guī)格。

圖3

具有R-2R內(nèi)部結(jié)構(gòu)的DAC表現(xiàn)出雙突短時(shí)毛刺脈沖干擾

圖3中的代碼轉(zhuǎn)換仍然是從7FFFh至8000h。

[page]

為了理解DAC短時(shí)毛刺脈沖干擾的源頭,我們必須首先定義主進(jìn)位轉(zhuǎn)換。在主進(jìn)位轉(zhuǎn)換點(diǎn)上,最高有效位 (MSB)從低變高時(shí), 較低的位從高變?yōu)榈停粗嗳?。其中一個(gè)此類代碼變換示例就是0111b變?yōu)?000b,或者是從1000 000b變?yōu)?111 1111b的更加明顯的變化。

有些人也許會(huì)認(rèn)為這一現(xiàn)象在DAC的輸出表現(xiàn)出巨大的電壓變化時(shí)出現(xiàn)。實(shí)際上,這并不是每個(gè)DAC編碼機(jī)制都會(huì)出現(xiàn)的情況。更多細(xì)節(jié)請(qǐng)見參考文獻(xiàn)1。

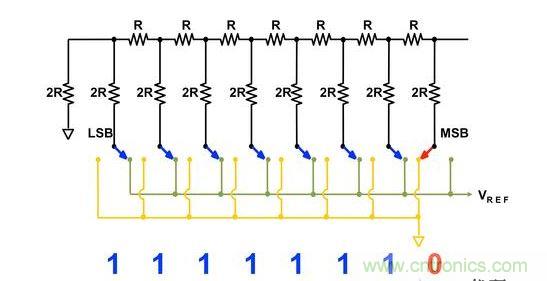

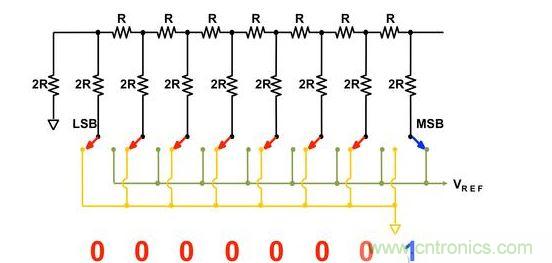

圖4和圖5顯示了這種類型的毛刺脈沖對(duì)一個(gè)8位DAC的影響。對(duì)于DAC用戶來說,這一現(xiàn)象在單個(gè)最低有效位 (LSB) 步長(zhǎng)時(shí)出現(xiàn),或者在一個(gè)5V、8位系統(tǒng)中,在19.5mV步長(zhǎng)時(shí)出現(xiàn)。

圖4

在這個(gè)8位DAC配置中,此內(nèi)部開關(guān)有7個(gè)R-2R引腳被接至VREF,有1個(gè)R-2R引腳接地。

圖5

在這個(gè)DAC配置中,此內(nèi)部開關(guān)有1個(gè)R-2R引腳被接至VREF,有7個(gè)R-2R引腳接地。

在DAC載入代碼時(shí),會(huì)有兩個(gè)區(qū)域產(chǎn)生輸出毛刺脈沖:同時(shí)觸發(fā)多個(gè)開關(guān)的開關(guān)同步和開關(guān)電荷轉(zhuǎn)移。

此電阻串DAC具有一個(gè)單開關(guān)拓?fù)洹R粋€(gè)電阻串DAC抽頭連接到巨大電阻串的不同點(diǎn)。開關(guān)網(wǎng)絡(luò)不需要主進(jìn)位上的多個(gè)轉(zhuǎn)換,因此,產(chǎn)生毛刺脈沖的可能進(jìn)性較低。開關(guān)電荷將會(huì)產(chǎn)生一個(gè)較小的毛刺脈沖,但是與R-2R結(jié)構(gòu)DAC產(chǎn)生的毛刺脈沖相比就顯得微不足道了。

[page]

代碼轉(zhuǎn)換期間,R-2R DAC具有多個(gè)同時(shí)開關(guān)切換。任何同步的缺失都導(dǎo)致短時(shí)間的開關(guān)全為高電平或全為低電平,從而使得DAC的電壓輸出遷移至電壓軌。然后這些開關(guān)恢復(fù),在相反的方向上產(chǎn)生一個(gè)單突短時(shí)毛刺脈沖干擾。然后輸出穩(wěn)定。

這些毛刺脈沖的電壓位置是完全可預(yù)計(jì)的。在使用R-2R DAC時(shí),最糟糕的情況是毛刺脈沖誤差出現(xiàn)在所有數(shù)字位切換,同時(shí)仍然用小電壓變化進(jìn)行轉(zhuǎn)換時(shí)。在這種情況下,用主進(jìn)位轉(zhuǎn)換進(jìn)行DAC代碼變化;從代碼1000…變換為0111…。

檢查真實(shí)DAC運(yùn)行狀態(tài)

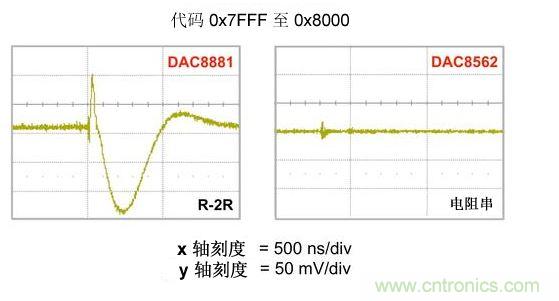

現(xiàn)在,我們已經(jīng)定義了針對(duì)短時(shí)毛刺脈沖干擾誤差的備選代碼轉(zhuǎn)換,我們可以仔細(xì)觀察一下16位DAC8881(R-2R DAC) 和16位DAC8562(電阻串DAC)的R-2R和電阻串DAC短時(shí)毛刺脈沖干擾。

在圖6中,DAC8881的短時(shí)毛刺脈沖干擾為37.7 nV-sec,而DAC8562的短時(shí)毛刺脈沖干擾為0.1 nV-sec。在這兩張圖中,x軸的刻度為500ns/div,而y軸的刻度為50mV/div。

圖6

R-2R和電阻串短時(shí)毛刺脈沖干擾性能

毛刺脈沖消失了

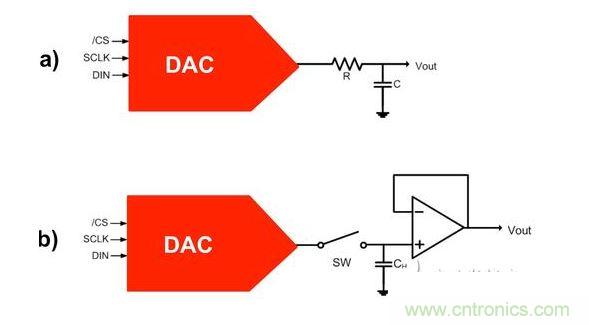

如果存在DAC短時(shí)毛刺脈沖干擾問題,用戶可以使用外部組件來減小毛刺脈沖幅度(圖7a),或者完全消除短時(shí)毛刺脈沖干擾能量(圖7b。)

圖7

用一階低通濾波器 (a) 或采樣/保持解決方案 (b) 來減少短時(shí)毛刺脈沖干擾誤差。

DAC之后的RC濾波器可減少毛刺脈沖幅度(圖7a)。短時(shí)毛刺脈沖干擾周期決定了適當(dāng)?shù)腞C比。RC濾波器3dB的頻率比短時(shí)毛刺脈沖干擾頻率提前十倍頻。在選擇組件時(shí)需要確保電阻器的電阻值較低,否則的它將會(huì)與電阻負(fù)載一起產(chǎn)生一個(gè)壓降。由于毛刺脈沖能量從不會(huì)丟失,執(zhí)行單極低通濾波器的代價(jià)就是在穩(wěn)定時(shí)間加長(zhǎng)的同時(shí)誤差被分布在更長(zhǎng)的時(shí)間段內(nèi)。

第二種方法是使用一個(gè)采樣/保持電容器和放大器(圖7b)。外部開關(guān)和放大器消除了DAC內(nèi)部開關(guān)產(chǎn)生的毛刺脈沖,從而獲得較小的采樣/保持 (S/H) 開關(guān)瞬態(tài)。在這個(gè)設(shè)計(jì)中,開關(guān)在DAC的整個(gè)主進(jìn)位轉(zhuǎn)換期間保持打開狀態(tài)。一旦轉(zhuǎn)換完成,開關(guān)關(guān)閉,從而在CH采樣電容器上設(shè)定新輸出電壓。當(dāng)DAC準(zhǔn)備升級(jí)其輸出時(shí),此電容器在外部開關(guān)打開時(shí)繼續(xù)保持新電壓。這個(gè)解決方案成本較高,也會(huì)占據(jù)更多的板級(jí)空間,但能夠在不增加穩(wěn)定時(shí)間的情況下減少/消除毛刺脈沖。