【導(dǎo)讀】與ECL、PECL和CML等高速信號分配相關(guān)的標(biāo)準(zhǔn)相比,ANSI EIA/TIA-644的低電壓差分信號(LVDS)標(biāo)準(zhǔn)具有低功耗、低噪聲輻射等優(yōu)勢。本應(yīng)用筆記對比了這些通信標(biāo)準(zhǔn)的特性,并討論了LVDS標(biāo)準(zhǔn)的優(yōu)勢。

引言

隨著微處理器、DSP和數(shù)字ASIC時鐘頻率的提高,背板信號的通信速率也在不斷提高。較快的時鐘速率使得基于TTL的單端信號的弱點(diǎn)越來越突出,主要表現(xiàn)在:功耗增大、抖動(導(dǎo)致誤碼)、高電平輻射、傳輸線效應(yīng)(如阻抗失配和串?dāng)_)、電源去耦難度增大以及其它一些問題。盡管一般認(rèn)為利用該技術(shù)速率能夠保持在50MHz以上,但是,上述問題迫使設(shè)計(jì)人員尋求更為有效的解決方案。

提高所有總線和/或背板帶寬的一個方法是增加總線寬度,但采用這種方法會增大PCB布局難度,而且需要引腳數(shù)非常多的連接器,導(dǎo)致系統(tǒng)成本提高、而且非常笨重。當(dāng)距離超出幾個厘米時,采用串行通信方式是解決上述問題的一個有效方案。高速數(shù)據(jù)通信系統(tǒng),如3G基站、路由器、加載/卸載復(fù)用器及其它設(shè)備,采用串行通信方式能夠獲得很大收益。

采用低壓差分信號(LVDS)替代TTL信號,能夠降低背板通信的誤碼率、串?dāng)_和輻射。

LVDS、ECL、PECL和CML的特征

LVDS在需要信號完整性、低抖動(抖動定義為信號的輸出跳變時間與理想值的偏差)及較高共模特性的高速系統(tǒng)中得到了越來越廣泛的應(yīng)用。LVDS是目前用于高速串行接口的有效方案之一。

其它標(biāo)準(zhǔn)包括(由低速到高速排列):ECL (射極耦合邏輯)、PECL (正ECL)、CML (電流模式邏輯),這些標(biāo)準(zhǔn)均采用差分信號。

ECL是傳統(tǒng)的高速邏輯標(biāo)準(zhǔn),它基于雙極型晶體差分對管,采用負(fù)偏置電源。PECL由ECL發(fā)展而來,采用正電源。新一代的ECL器件具有200ps左右的延遲時間,可應(yīng)用于頻率大于3GHz的系統(tǒng)。

在現(xiàn)有的接口標(biāo)準(zhǔn)中,CML的工作速率最高,可用于千兆位數(shù)據(jù)速率的系統(tǒng)。與其它標(biāo)準(zhǔn)相比,CML還具有一個額外的優(yōu)勢:集成了一個50Ω匹配電阻,大大簡化了實(shí)現(xiàn)良好匹配的設(shè)計(jì)。但是當(dāng)鏈路每個端點(diǎn)工作在不同的電源電壓時,需外接耦合元件。

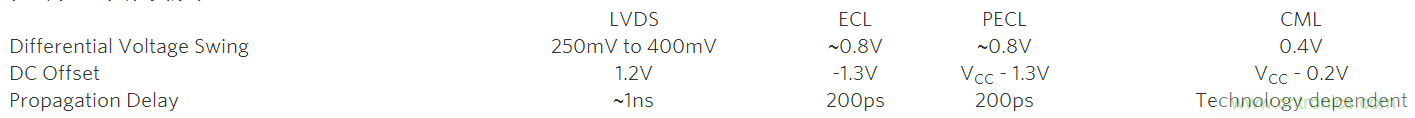

本文主要討論LVDS的特性及其可能的應(yīng)用,表1列出了LVDS的一些特性參數(shù)以及與ECL、PECL和CML系統(tǒng)的對比結(jié)果。按照EIA/TIA-644 LVDS和IEEE® 1596.3標(biāo)準(zhǔn)規(guī)定,LVDS采用差分信號,信號幅度范圍為250mV至400mV、直流偏置1.2V。

表1. 高速通信系統(tǒng)的對比*

*ECL和PECL發(fā)送器輸出信號的擺幅高于LVDS發(fā)送器的信號擺幅,較高的輸出擺幅和較短的傳輸延時使得ECL和PECL器件具有更高的功耗。

LVDS的優(yōu)勢

LVDS的差分特性為其帶來了許多優(yōu)點(diǎn):抑制共模噪聲、理論上自身不產(chǎn)生噪聲(假設(shè)差分信號完全對稱,即正、負(fù)輸出之間沒有畸變)。LVDS能夠用CMOS工藝實(shí)現(xiàn),便于同其它電路一起集成。

由于LVDS采用差分信號,因此吸取電源電流的峰值較低,只需加適當(dāng)?shù)娜ヱ铍娙菁纯山鉀Q電源去耦問題。通常LVDS消耗的功率低于ECL和CML,當(dāng)然,在某種程度上這取決于所采用的匹配方案。

LVDS的應(yīng)用

LVDS大多用于時鐘分配和多個單點(diǎn)至單點(diǎn)的信號分配。時鐘分配對于不同子系統(tǒng)需要同一參考時鐘的數(shù)字系統(tǒng)非常重要,例如:多數(shù)情況下基站的DSP需要與射頻信號處理電路同步,利用鎖相環(huán)(PLL)產(chǎn)生所需要的本振頻率,ADC被鎖存到中心參考時鐘。當(dāng)與無線接收機(jī)一起工作時,還必須以盡可能低的輻射分配時鐘(和信號),以避免對小信號通路的干擾。

把高速信號分配給不同單元時可以采用不同的策略,其中有兩種極端情況:一種是將一路信號源/驅(qū)動器的信號分配給所有單元(稱為多點(diǎn)分配器);另一種是對每一個單元采用一個獨(dú)立的驅(qū)動器(稱為多個單點(diǎn)至單點(diǎn)分配器)。圖1說明了這兩種分配架構(gòu)的區(qū)別。對于多點(diǎn)分配器,驅(qū)動器要保證足以驅(qū)動所有的接收器和傳輸媒介(電纜、連接器、背板),總線通常需要在末級接收器加匹配阻抗。所有分支與總線的距離必須盡可能短,以避免引起信號完整性問題,在高密度PCB普遍應(yīng)用的今天,較好地控制分支長度并非易事。

圖1. 多點(diǎn)信號分配允許一個發(fā)送器與多個接收器之間的通信;多個單點(diǎn)至單點(diǎn)信號分配不需要中間接頭,也消除了接頭產(chǎn)生的干擾。

多個單點(diǎn)至單點(diǎn)分配結(jié)構(gòu)中需要多路驅(qū)動器,可定義為點(diǎn)到點(diǎn)的操作,每路驅(qū)動器與一路本地終端接收機(jī)之間通信。這種結(jié)構(gòu)減少了信號完整性問題,能夠保證傳輸媒介的阻抗盡可能一致,消除了多條支路產(chǎn)生的干擾。

本文來源于Maxim。

推薦閱讀: