【導讀】內(nèi)插器可以很好地節(jié)省器件成本,在這里,可以將無源器件嵌入進來從而降低整體封裝尺寸。像電容、電阻、電感這樣的無源器件會占據(jù)超過50%的寶貴晶片面積,所以如果把它們從處理器的管芯上移除掉,會讓集成整合更加高效。但是這就能解圍3D封裝的遲遲不來嗎?

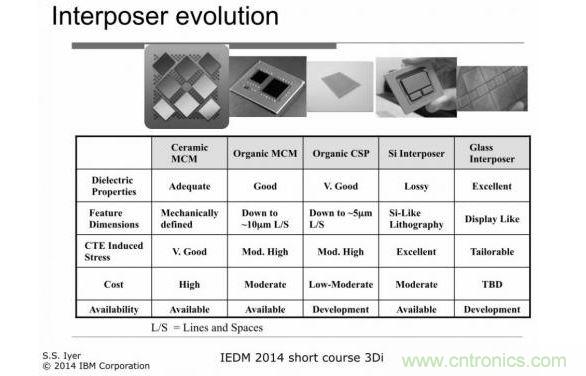

IEDM 2014會議期間提供了一些課程教材,其中,關(guān)于3D IC的幻燈片引起了我的注意。下面圖中幻燈片給出了關(guān)于半導體行業(yè)中所使用的不同內(nèi)插器的概述。

在這個教程中,我看到了大家關(guān)于內(nèi)插器怎樣改變半導體行業(yè)的一些討論。在早期,內(nèi)插器的功用在于可以使器件擁有非常大的IO數(shù)量,這樣一來內(nèi)插器是作為層疊平臺的擴充套件形式存在的,但現(xiàn)在,它可以很好地節(jié)省器件成本,在這里,可以將無源器件嵌入進來從而降低整體封裝尺寸。像電容、電阻、電感這樣的無源器件會占據(jù)超過50%的寶貴晶片面積,所以如果把它們從處理器的管芯上移除掉,會讓集成整合更加高效。這張幻燈片讓我想到在一個內(nèi)插器中集成無源器件(IPD)及其成本評估。我很想知道,是否會有芯片制造商染指這個領(lǐng)域。

我發(fā)現(xiàn),2014年的IEDM大會上有一篇來自臺積電的論文,在文中他們描述了采用銅鑲嵌工藝在硅內(nèi)插器上實現(xiàn)的一種MIM電容。硅內(nèi)插器具有從頂部和底部兩側(cè)連接到外部器件的能力。在最頂部金屬層的上面,有一個重分布的層連接到一個u型凸點上,有助于和處理器管芯的連接。而在基片的底部,一個硅通孔連接到一個C4凸塊焊盤上,從而附著到封裝基板上。相信這應該是目前在硅內(nèi)插器上嵌入無源器件的最尖端的案例。

接下來我又搜索了關(guān)于在玻璃襯底上嵌入無源器件的資料。玻璃襯底一直在吸引大量的關(guān)注,特別是在高頻應用中,因為玻璃可以在跨度很大的工作頻率和溫度區(qū)間內(nèi)保持低損的特性。這種技術(shù)的主要玩家有佐治亞理工學院、IMEC、意法半導體、弗勞恩霍夫研究所、肖特集團、旭硝子與道康寧。所有這些公司都在玻璃內(nèi)插器上進行了深入的研發(fā),而且所有公司都在玻璃襯底上制造了無源器件,并在若干個會議中展示了他們的研究成果。大多數(shù)情況下,會在玻璃襯底上沉積一層有機體,然后在這個有機層上生產(chǎn)無源器件。佐治亞理工學院的網(wǎng)站上同樣展示了采用玻璃通孔工藝的無源器件。

不過,可能是因為我搜索的資料有限,我并沒有找到在一個內(nèi)插器上實現(xiàn)的帶有IPD的商業(yè)化芯片,這樣的芯片中,內(nèi)插器是連接到處理器上的。如果是這樣,這實際上是一種2.5D的集成方案,對玻璃襯底也是如此。由于存在一些固有的制造挑戰(zhàn),在這個方案上,玻璃內(nèi)插器落后于硅內(nèi)插器。比如,你可以在硅襯底上應用所有已知的半導體行業(yè)的專業(yè)知識。采用先進的印刷技術(shù)可以將精細的尺寸圖案化,在硅襯底上可以實施高密度的硅通孔,而且載體晶圓可以很容易做到厚度低于50微米。而對于玻璃而言,卻很難應用這些技術(shù),把玻璃襯底削薄也充滿了挑戰(zhàn)。然而,玻璃也并非一無是處,它也存在一些優(yōu)勢屬性:它可以做到900毫米x900毫米,這樣一來這些大型面板便可以產(chǎn)生非常高數(shù)量的玻璃內(nèi)插基板,這比從300毫米的硅晶圓上切割出的硅內(nèi)插器的數(shù)量要高出一個量級,從而降低了這些玻璃基板的整體價格。而且,玻璃的低損耗特性非常適合于高頻應用,尤其是電感一類的無源器件。當然,硅和玻璃這兩種材料都各有自己的優(yōu)缺點。

基于研究和會議記錄,很顯然,半導體行業(yè)將使用嵌入無源器件的內(nèi)插器以實現(xiàn)小型化和增加功能。這個進程可能會因為生產(chǎn)良率、測試和質(zhì)量標準以及可靠性等問題而有所拖延。

處理器是一種高質(zhì)量規(guī)格的產(chǎn)品,如果我們把它連接到一個實現(xiàn)了無源器件的內(nèi)插器,可能會帶來一些額外的可靠性考慮,特別是處理器和內(nèi)插器的連接處的可靠性。嵌入式組件進行返工是不大現(xiàn)實的,所以嵌入式無源器件具有很高的良率至關(guān)重要。我們知道在系統(tǒng)級封裝(SIP)中嵌入無源器件的重要性,所以行業(yè)將很快確定最具成本效益的2.5D集成工藝。大型芯片制造商、研究組織和OSAT成員在內(nèi)插器上進行了大量的研發(fā)活動,所以,很可能,我們不用等太久就可以看到在內(nèi)插器中實現(xiàn)IPD的商業(yè)產(chǎn)品成為主流。