【導讀】鑒于內(nèi)核、存儲器、I/O 以及其它電軌的過多電壓電流要求,多核 DSP 實施需要智能電源管理。DSP 內(nèi)核電壓電源的一個重要性能基準就是能夠根據(jù)DSP 使用情況及環(huán)境條件實時調(diào)節(jié) VCORE。VCORE 命令一般以數(shù)字格式提供,電源應能隨時解讀。VCORE 電軌一般具有最大的電流規(guī)范,而能夠平衡效率與尺寸的小型電源解決方案也很重要。關鍵在于在 DSP 與模擬 PWM 級之間使用低成本接口來實現(xiàn)這一電壓識別 (VID) 功能。

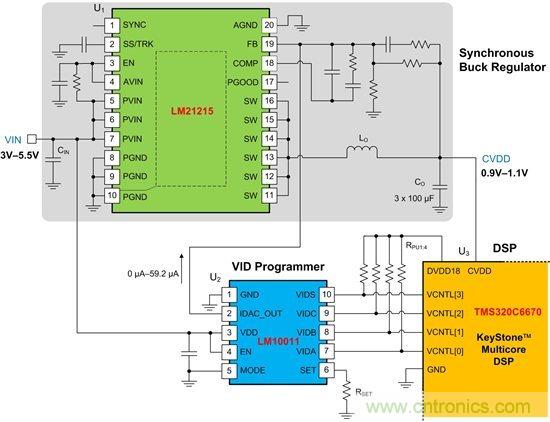

因此,下圖提供了將內(nèi)核電軌標示為 CVDD 的多核 DSP 加以說明。

一個額定電流為 15A 的 500KHz 降壓轉(zhuǎn)換器負責為 CVDD 供電。該設計可使用連接至 VID 編程器的 4 線數(shù)字接口實現(xiàn) VID 控制,其可直接連接至任何模擬功率級或控制器。點擊這里觀看 VID 編程器的視頻演示。

KeyStone DSP 與 VID 功能同步降壓轉(zhuǎn)換器的原理圖

LM10011 與模擬 PWM 功率級

LM10011 不僅可采集出現(xiàn)在 DSP VCNTL 接口上的 VID 信息,而且還可設置連接至功率級電路反饋 (FB) 引腳的電流 DAC 輸出。在 6 位模式下,既提供支持 940nA 分辨率的 64 種電流設置,又提供優(yōu)于 1% 的誤差精度。在本例中,CVDD 由 DSP 判定為一個電壓介于 0.9V 至 1.1V 之間的電平,支持 6.4mV 的步進分辨率。無需電平轉(zhuǎn)換器或膠合邏輯,電阻器 RSET 可決定啟動時的 CVDD 電壓。LM10011 可與任何具有 FB 輸入的電壓、電流或 DCAP 模式 PWM 調(diào)節(jié)器連接。

推薦閱讀: