【導(dǎo)讀】使用時(shí)鐘分配器件1或者扇出緩沖器為ADC 和DAC 提供時(shí)鐘時(shí)�����,需要考慮印刷電路板上的走線和輸出端接�,這是信號(hào)衰減的兩個(gè)主要來源�。

時(shí)鐘走線與信號(hào)擺幅

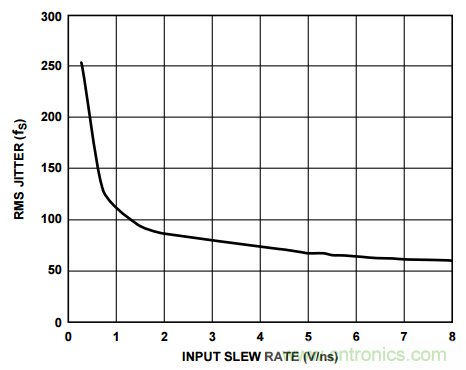

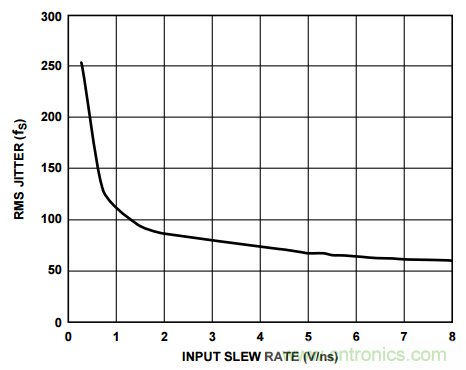

PCB 上的走線類似于低通濾波器,當(dāng)時(shí)鐘信號(hào)沿著走線傳輸時(shí)�,會(huì)造成時(shí)鐘信號(hào)衰減���,并且脈沖沿的失真隨線長(zhǎng)增加���。更高的時(shí)鐘信號(hào)頻率會(huì)導(dǎo)致衰減�、失真和噪聲增加��,但不會(huì)增加抖動(dòng)��,在低壓擺率時(shí)抖動(dòng)最大(圖 1)�,一般使用高壓擺率的時(shí)鐘沿。為了實(shí)現(xiàn)高質(zhì)量的時(shí)鐘����,要使用高擺幅時(shí)鐘信號(hào)和短時(shí)鐘 PCB 走線;由時(shí)鐘驅(qū)動(dòng)的器件應(yīng)該盡可能靠近時(shí)鐘分配器件放置�。

圖 1. ADCLK925 的均方根抖動(dòng)與輸入壓擺率的關(guān)系

ADCLK9542 時(shí)鐘扇出緩沖器和 ADCLK9143 超快時(shí)鐘緩沖器就是兩款此類時(shí)鐘分配器件。ADCLK954 包括 12 個(gè)輸出驅(qū)動(dòng)���,可以在 50-?的負(fù)載上驅(qū)動(dòng)全擺幅為 800-mV 的 ECL(發(fā)射極耦合邏輯)或者 LVPECL(低壓正 ECL)信號(hào)��,形成 1.6 V 的總差分輸出擺幅�,如圖2 所示���。它可以在4.8 GHz 反轉(zhuǎn)率下工作����。ADCLK914 可以在 50-?負(fù)載上驅(qū)動(dòng) 1.9 V 高壓差分信號(hào) (HVDS),形成 3.8 V 的總差分輸出擺幅�。ADCLK914 具有7.5-GHz 的反轉(zhuǎn)率。

當(dāng)驅(qū)動(dòng) DAC 時(shí)�,時(shí)鐘分配器件應(yīng)該盡可能靠近 DAC 的時(shí)鐘輸入放置,這樣����,所需的高壓擺率、高幅度時(shí)鐘信號(hào)才不會(huì)引起布線困難���、產(chǎn)生 EMI 或由電介質(zhì)和其它損耗造成減弱�����。值得注意的是�,走線的特性阻抗(Z0)會(huì)隨走線尺寸(長(zhǎng)度���、寬度和深度)而變化�;驅(qū)動(dòng)器的輸出阻抗必須與特性阻抗匹配����。

圖2. 采 用 3.3V 電 源供電時(shí) ADCLK954 時(shí) 鐘緩沖器的輸出波形

輸出端接

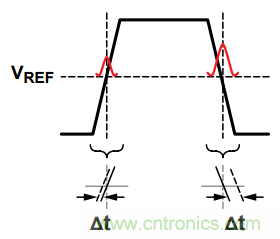

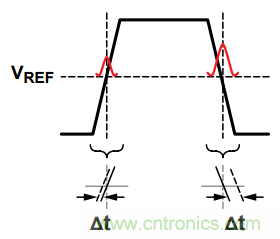

時(shí)鐘信號(hào)衰減會(huì)增加抖動(dòng)�����,因此對(duì)驅(qū)動(dòng)器輸出的端接很重要,這可以避免信號(hào)反射��,并可通過相對(duì)較大的帶寬實(shí)現(xiàn)最大能量傳輸����。確實(shí),反射可以造成下沖和過沖���,嚴(yán)重降低信號(hào)和整體時(shí)鐘的性能��,或者在極端情況下�����,可能會(huì)損壞接收器或驅(qū)動(dòng)器�����。反射因阻抗不匹配而引起���,在走線沒有適當(dāng)端接時(shí)發(fā)生��。由于反射系數(shù)本身具有高通特性�����,因此這對(duì)具有快速上升和下降時(shí)間的高速信號(hào)更重要�����。反射脈沖與主時(shí)鐘信號(hào)相疊加�����,削弱了時(shí)鐘脈沖���。如圖3 所示,它對(duì)上升沿和下降沿增加了不確定的延時(shí)或者抖動(dòng)����,從而影響時(shí)鐘信號(hào)的邊沿。

圖3. 由端接不當(dāng)引起的反射信號(hào)抖動(dòng)

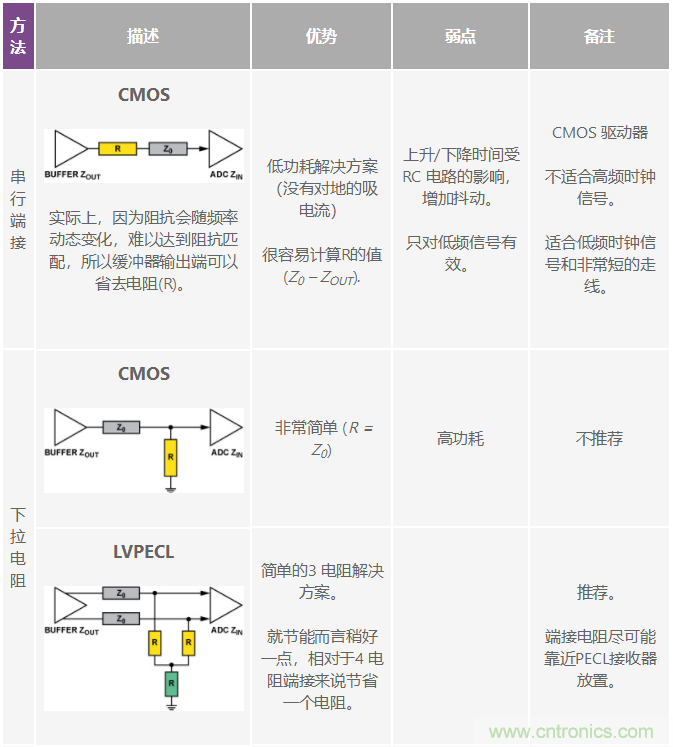

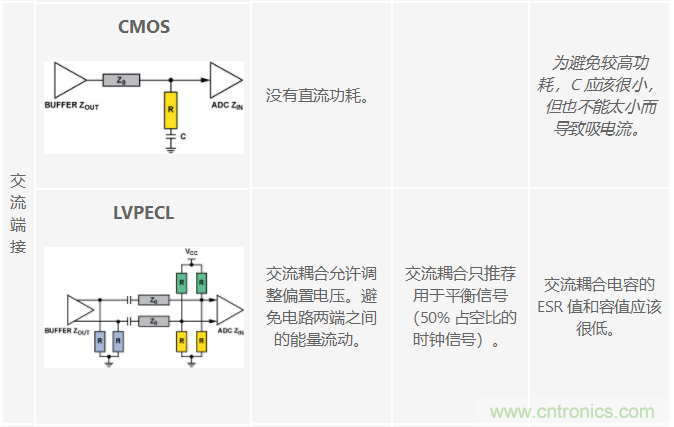

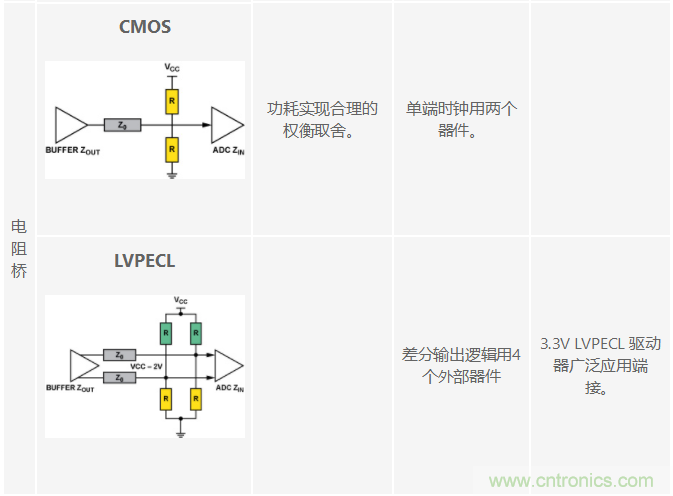

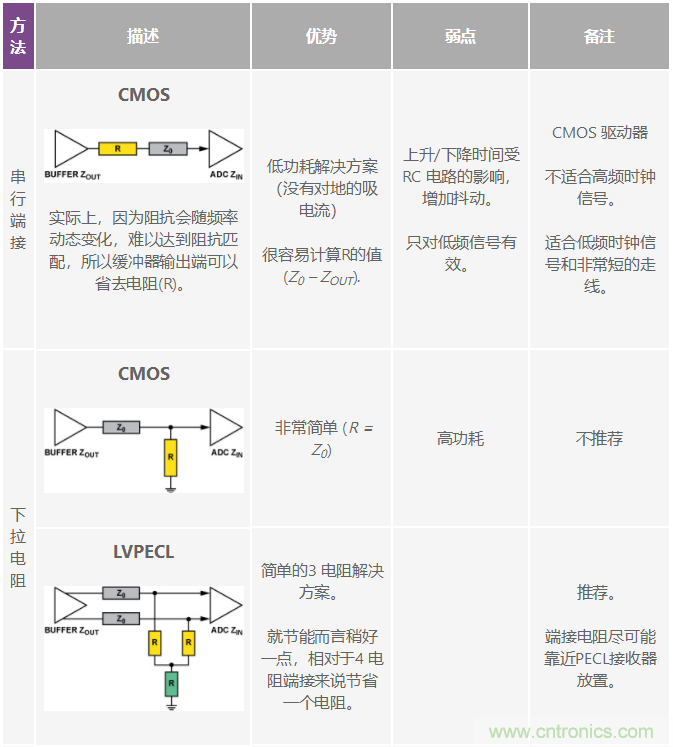

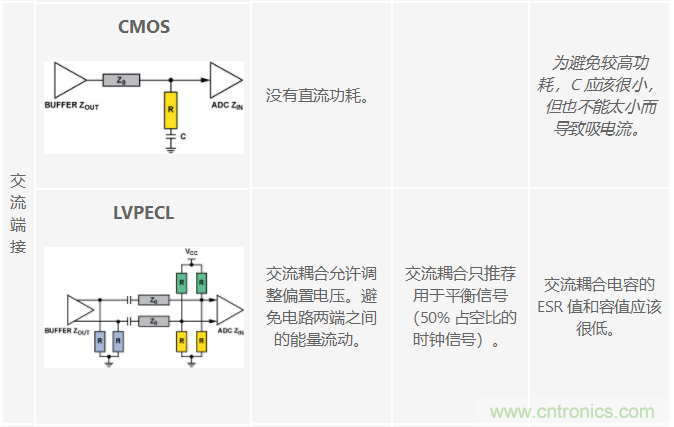

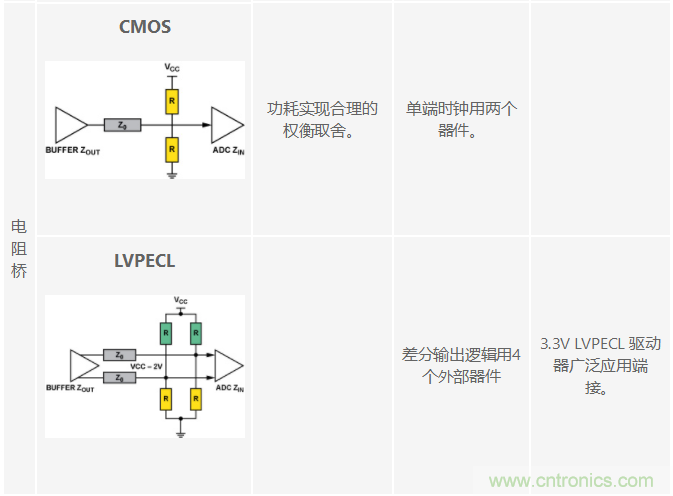

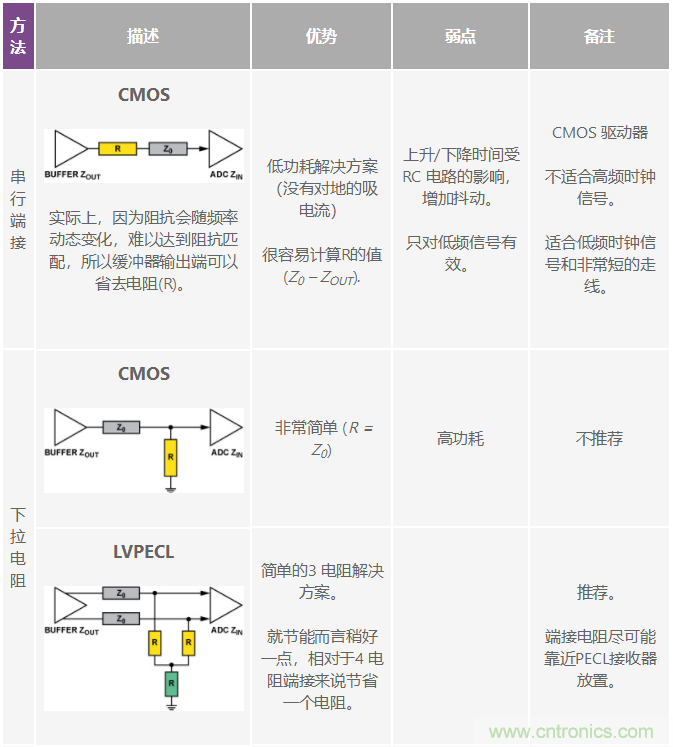

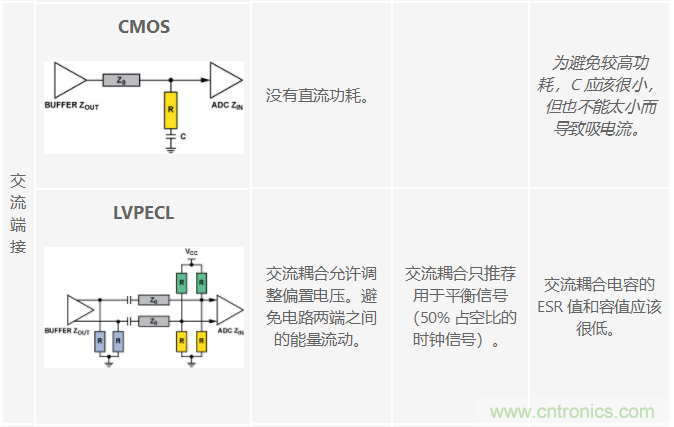

端接不當(dāng)使回聲的幅度隨著時(shí)間而變化�,因此?t 也會(huì)隨時(shí)間變化。端接的時(shí)間常數(shù)也會(huì)影響回聲脈沖的形狀和寬度���?��;谝陨显?�,反射引起的附加抖動(dòng)���,從形狀看類似增加經(jīng)典抖動(dòng)的高斯特性。為了避免抖動(dòng)和時(shí)鐘質(zhì)量降低的不利影響����,需要使用表 1 中總結(jié)的恰當(dāng)信號(hào)端接方法�����。Z0 是傳輸線的阻抗���; ZOUT 是驅(qū)動(dòng)器的輸出阻抗���, ZIN 是接收器的輸入阻抗。顯示CMOS 和 PECL/LVPECL電路���。

表1. 時(shí)鐘端接

參考電路

1www.analog.com/en/products/clock-and-timing/clock-generation-distribution.html.

2www.analog.com/en/clock-and-timing/clock-generation-and-distribution/adclk954/products/product.html.

3www.analog.com/en/clock-and-timing/clock-generation-and-distribution/adclk914/products/product.html.

推薦閱讀: