【導(dǎo)讀】DC/DC 開關(guān)控制器的 MOSFET 選擇是一個(gè)復(fù)雜的過程。僅僅考慮 MOSFET 的額定電壓和電流并不足以選擇到合適的 MOSFET。要想讓 MOSFET 維持在規(guī)定范圍以內(nèi),必須在低柵極電荷和低導(dǎo)通電阻之間取得平衡。在多負(fù)載電源系統(tǒng)中,這種情況會(huì)變得更加復(fù)雜。

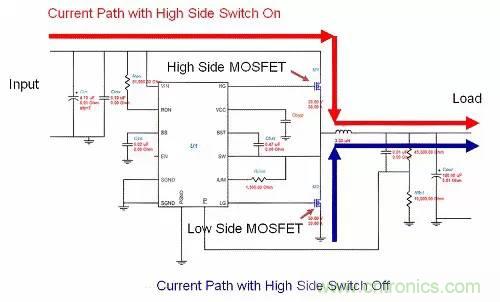

圖 1—降壓同步開關(guān)穩(wěn)壓器原理圖

DC/DC 開關(guān)電源因其高效率而廣泛應(yīng)用于現(xiàn)代許多電子系統(tǒng)中。例如,同時(shí)擁有一個(gè)高側(cè) FET和低側(cè) FET 的降壓同步開關(guān)穩(wěn)壓器,如圖 1 所示。這兩個(gè) FET 會(huì)根據(jù)控制器設(shè)置的占空比進(jìn)行開關(guān)操作,旨在達(dá)到理想的輸出電壓。降壓穩(wěn)壓器的占空比方程式如下:

1) 占空比 (高側(cè)FET,上管) = Vout/(Vin*效率)

2) 占空比 (低側(cè)FET,下管) = 1 – DC (高側(cè)FET)

FET 可能會(huì)集成到與控制器一樣的同一塊芯片中,從而實(shí)現(xiàn)一種最為簡單的解決方案。但是,為了提供高電流能力及(或)達(dá)到更高效率,F(xiàn)ET 需要始終為控制器的外部元件。這樣便可以實(shí)現(xiàn)最大散熱能力,因?yàn)樗孎ET物理隔離于控制器,并且擁有最大的 FET 選擇靈活性。它的缺點(diǎn)是 FET 選擇過程更加復(fù)雜,原因是要考慮的因素有很多。

一個(gè)常見問題是“為什么不讓這種 10A FET 也用于我的 10A 設(shè)計(jì)呢?”答案是這種 10A 額定電流并非適用于所有設(shè)計(jì)。

選擇 FET 時(shí)需要考慮的因素包括額定電壓、環(huán)境溫度、開關(guān)頻率、控制器驅(qū)動(dòng)能力和散熱組件面積。關(guān)鍵問題是,如果功耗過高且散熱不足,則 FET 可能會(huì)過熱起火。我們可以利用封裝/散熱組件 ThetaJA 或者熱敏電阻、FET 功耗和環(huán)境溫度估算某個(gè) FET 的結(jié)溫,具體方法如下:

3) Tj = ThetaJA * FET 功耗(PdissFET) + 環(huán)境溫度(Tambient)

它要求計(jì)算 FET 的功耗。這種功耗可以分成兩個(gè)主要部分:AC 和 DC 損耗。這些損耗可以通過下列方程式計(jì)算得到:

4) AC損耗: AC 功耗(PswAC) = ½ * Vds * Ids * (trise + tfall)/Tsw

其中,Vds 為高側(cè) FET 的輸入電壓,Ids 為負(fù)載電流,trise 和 tfall 為 FET 的升時(shí)間和降時(shí)間,而Tsw 為控制器的開關(guān)時(shí)間(1/開關(guān)頻率)。

5) DC 損耗: PswDC = RdsOn * Iout * Iout * 占空比

其中,RdsOn 為 FET 的導(dǎo)通電阻,而 Iout 為降壓拓?fù)涞呢?fù)載電流。

其他損耗形成的原因還包括輸出寄生電容、門損耗,以及低側(cè) FET 空載時(shí)間期間導(dǎo)電帶來的體二極管損耗,但在本文中我們將主要討論 AC 和 DC 損耗。

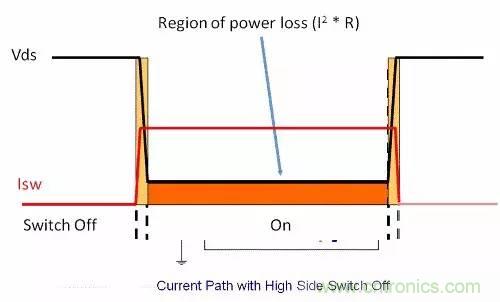

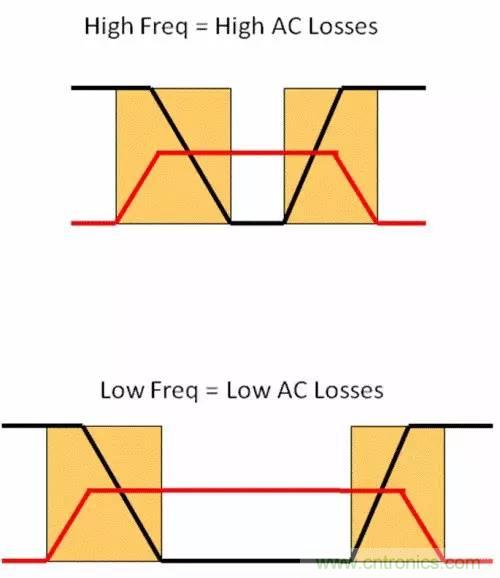

開關(guān)電壓和電流均為非零時(shí),AC 開關(guān)損耗出現(xiàn)在開關(guān)導(dǎo)通和關(guān)斷之間的過渡期間。圖 2 中高亮部分顯示了這種情況。根據(jù)方程式 4),降低這種損耗的一種方法是縮短開關(guān)的升時(shí)間和降時(shí)間。通過選擇一個(gè)更低柵極電荷的 FET,可以達(dá)到這個(gè)目標(biāo)。另一個(gè)因數(shù)是開關(guān)頻率。開關(guān)頻率越高,圖 3 所示升降過渡區(qū)域所花費(fèi)的開關(guān)時(shí)間百分比就越大。因此,更高頻率就意味著更大的AC開關(guān)損耗。所以,降低 AC 損耗的另一種方法便是降低開關(guān)頻率,但這要求更大且通常也更昂貴的電感來確保峰值開關(guān)電流不超出規(guī)范。

圖 2—AC 損耗圖

圖 3—開關(guān)頻率對(duì) AC 損耗的影響

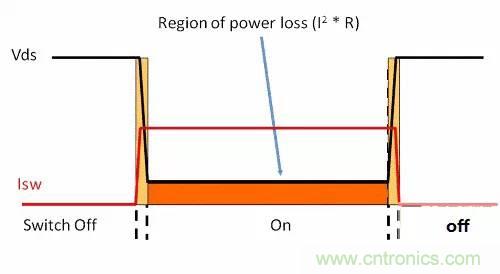

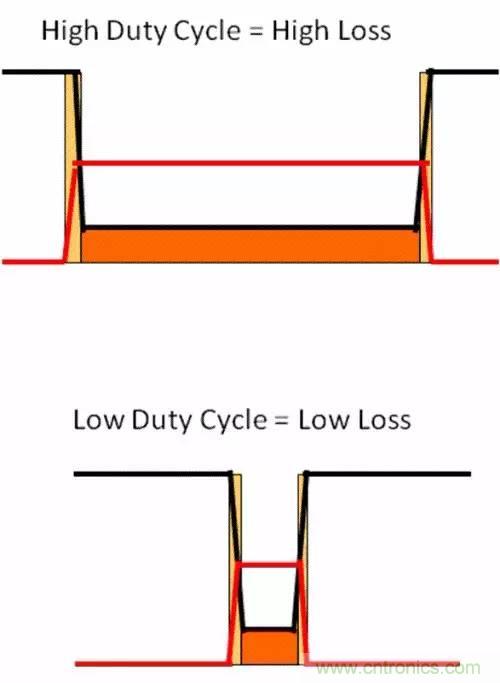

開關(guān)處在導(dǎo)通狀態(tài)下出現(xiàn) DC 損耗,其原因是 FET 的導(dǎo)通電阻。這是一種十分簡單的 I2R 損耗形成機(jī)制,如圖 4 所示。但是,導(dǎo)通電阻會(huì)隨 FET 結(jié)溫而變化,這便使得這種情況更加復(fù)雜。所以,使用方程式 3)、4)和 5)準(zhǔn)確計(jì)算導(dǎo)通電阻時(shí),就必須使用迭代方法,并要考慮到 FET 的溫升。降低 DC 損耗最簡單的一種方法是選擇一個(gè)低導(dǎo)通電阻的 FET。另外,DC 損耗大小同F(xiàn)ET 的百分比導(dǎo)通時(shí)間成正比例關(guān)系,其為高側(cè) FET控制器占空比加上 1 減去低側(cè) FET 占空比,如前所述。由圖 5 我們可以知道,更長的導(dǎo)通時(shí)間就意味著更大的DC 開關(guān)損耗,因此,可以通過減小導(dǎo)通時(shí)間/FET 占空比來降低 DC 損耗。例如,如果使用了一個(gè)中間 DC 電壓軌,并且可以修改輸入電壓的情況下,設(shè)計(jì)人員或許就可以修改占空比。

圖 4—DC 損耗圖

圖 5—占空比對(duì) DC 損耗的影響

盡管選擇一個(gè)低柵極電荷和低導(dǎo)通電阻的 FET 是一種簡單的解決方案,但是需要在這兩種參數(shù)之間做一些折中和平衡。低柵極電荷通常意味著更小的柵極面積/更少的并聯(lián)晶體管,以及由此帶來的高導(dǎo)通電阻。另一方面,使用更大/更多并聯(lián)晶體管一般會(huì)導(dǎo)致低導(dǎo)通電阻,從而產(chǎn)生更多的柵極電荷。這意味著,F(xiàn)ET 選擇必須平衡這兩種相互沖突的規(guī)范。另外,還必須考慮成本因素。

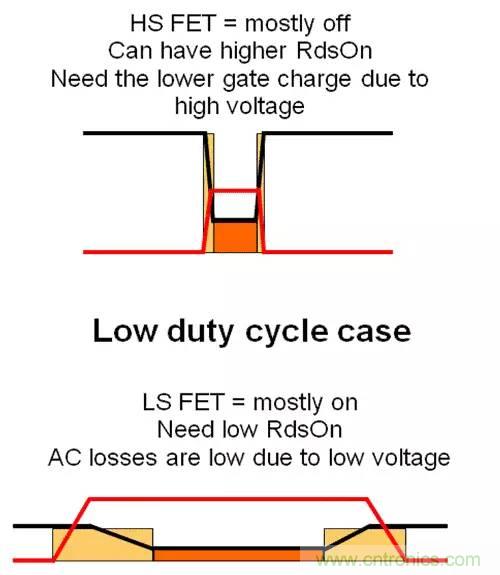

低占空比設(shè)計(jì)意味著高輸入電壓,對(duì)這些設(shè)計(jì)而言,高側(cè) FET 大多時(shí)候均為關(guān)斷,因此 DC 損耗較低。但是,高 FET 電壓帶來高 AC 損耗,所以可以選擇低柵極電荷的 FET,即使導(dǎo)通電阻較高。低側(cè) FET 大多數(shù)時(shí)候均為導(dǎo)通狀態(tài),但是 AC 損耗卻最小。這是因?yàn)椋瑢?dǎo)通/關(guān)斷期間低側(cè) FET 的電壓因 FET 體二極管而非常地低。因此,需要選擇一個(gè)低導(dǎo)通電阻的 FET,并且柵極電荷可以很高。圖 7 顯示了上述情況。

圖 7—低占空比設(shè)計(jì)的高側(cè)和低側(cè) FET 功耗

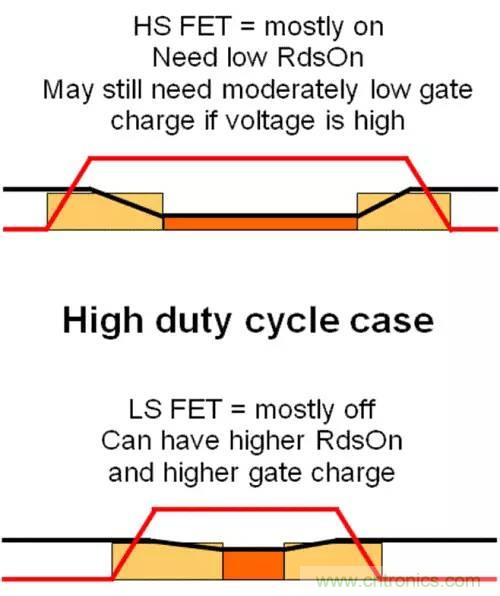

如果我們降低輸入電壓,則我們可以得到一個(gè)高占空比設(shè)計(jì),其高側(cè) FET 大多數(shù)時(shí)候均為導(dǎo)通狀態(tài),如圖 8 所示。這種情況下,DC 損耗較高,要求低導(dǎo)通電阻。根據(jù)不同的輸入電壓,AC 損耗可能并不像低側(cè) FET 時(shí)那樣重要,但還是沒有低側(cè) FET 那樣低。因此,仍然要求適當(dāng)?shù)牡蜄艠O電荷。這要求在低導(dǎo)通電阻和低柵極電荷之間做出妥協(xié)。就低側(cè) FET 而言,導(dǎo)通時(shí)間最短,且 AC 損耗較低,因此我們可以按照價(jià)格或者體積而非導(dǎo)通電阻和柵極電荷原則,選擇正確的 FET。

圖 8—高占空比設(shè)計(jì)的高側(cè)和低側(cè) FET 功耗

假設(shè)一個(gè)負(fù)載點(diǎn) (POL) 穩(wěn)壓器時(shí)我們可以規(guī)定某個(gè)中間電壓軌的額定輸入電壓,那么最佳解決方案是什么呢,是高輸入電壓/低占空比,還是低輸入電壓/高占空比呢?使用不同輸入電壓對(duì)占空比進(jìn)行調(diào)制,同時(shí)查看 FET功耗情況。

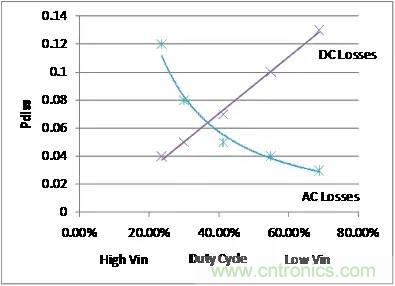

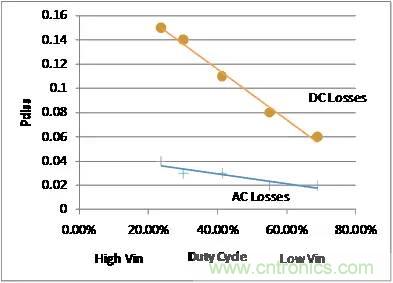

圖 9 中,高側(cè) FET 反應(yīng)曲線圖表明,占空比從 25% 增至 40% 時(shí) AC 損耗明顯降低,而DC 損耗卻線性增加。因此,35% 左右的占空比,應(yīng)為選擇電容和導(dǎo)通電阻平衡FET的理想值。不斷降低輸入電壓并提高占空比,可以得到最低的AC 損耗和最高的 DC 損耗,就此而言,我們可以使用一個(gè)低導(dǎo)通電阻的 FET,并折中選擇高柵極電荷。如低側(cè) FET 圖 10 所示,控制器占空比由低升高時(shí) DC 損耗線性降低(低側(cè) FET 導(dǎo)通時(shí)間更短),高控制器占空比時(shí)損耗最小。整個(gè)電路板的AC 損耗都很低,因此任何情況下都應(yīng)選擇使用低導(dǎo)通電阻的 FET。

圖 9—高側(cè)FET 損耗與占空比的關(guān)系

圖 10—低側(cè) FET 損耗與控制器占空比的關(guān)系。

請(qǐng)注意:低側(cè) FET 占空比為 1-控制器占空比,因此低側(cè) FET 導(dǎo)通時(shí)間隨控制器占空比增加而縮短

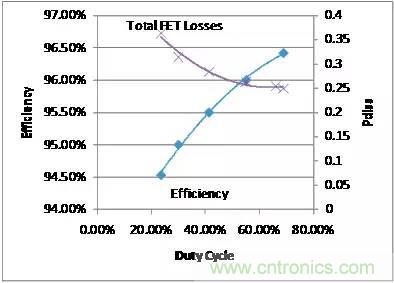

圖 11 顯示了我們將高側(cè)和低側(cè)損耗組合到一起時(shí)總效率的變化情況。我們可以看到,這種情況下,高占空比時(shí)組合 FET 損耗最低,并且效率最高。效率從 94.5% 升高至 96.5%。不幸的是,為了獲得低輸入電壓,我們必須降低中間電壓軌電源的電壓,使其占空比增加,原因是它通過一個(gè)固定輸入電源供電。因此,這樣可能會(huì)抵消在 POL 獲得的部分或者全部增益。另一種方法是不使用中間軌,而是直接從輸入電源到 POL 穩(wěn)壓器,目的是降低穩(wěn)壓器數(shù)。這時(shí),占空比較低,我們必須小心地選擇 FET。

圖 11—總損耗與效率和占空比的關(guān)系

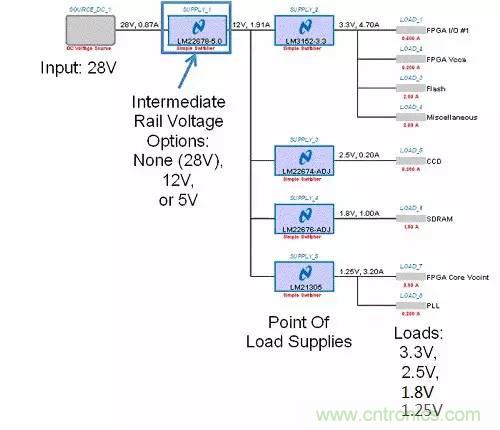

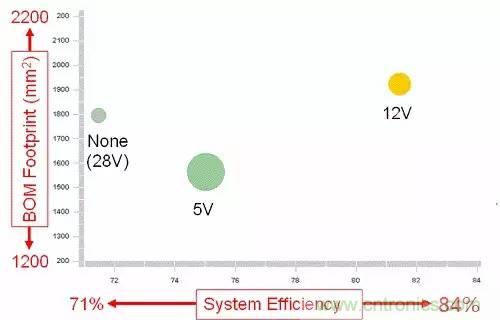

在有多個(gè)輸出電壓和電流要求的電源系統(tǒng)中,情況會(huì)更加復(fù)雜。對(duì)比不同 POL 穩(wěn)壓器占空比的效率、成本和體積。圖 12 顯示了一個(gè)系統(tǒng),其輸入電壓為 28V,共有 8 個(gè)負(fù)載,4 個(gè)不同電壓,范圍為 3.3V 到 1.25V。共有 3 種對(duì)比方法:1)無中間軌,直接通過輸入電源提供 28V 電壓,以實(shí)現(xiàn) POL 穩(wěn)壓器的低占空比;2)使用 12V 中間軌,POL穩(wěn)壓器中等占空比;3)使用 5V 中間軌,高 POL 穩(wěn)壓器占空比。圖 13 和表 1 顯示了對(duì)比結(jié)果。這種情況下,無中間軌電源的構(gòu)架實(shí)現(xiàn)了最低成本,12V中間軌電壓的構(gòu)架獲得了最高效率,而 5V 中間軌電壓構(gòu)架則實(shí)現(xiàn)了最小體積。因此,我們可以看到,對(duì)于這種大型系統(tǒng)而言,單POL電源情況下我們所看到的這些參數(shù)均沒有明顯的趨向。這是因?yàn)?,使用多個(gè)穩(wěn)壓器時(shí),除中間軌穩(wěn)壓器本身以外,每個(gè)穩(wěn)壓器都有其不同的負(fù)載電流和電壓要求,而這些需求可能會(huì)相互沖突。研究這種情況的最佳方法是使用如 WEBENCH 電源設(shè)計(jì)師等工具,對(duì)不同的選項(xiàng)進(jìn)行評(píng)估

圖 12—輸入、中間軌、負(fù)載點(diǎn) (POL) 電源和負(fù)載的電源系統(tǒng)

中間軌電壓的不同選擇為 28V(直接使用輸入電源)、12V 和 5V。這會(huì)帶來不同的 POL 穩(wěn)壓器占空比。

圖 13 電源設(shè)計(jì)曲線圖

其表明中間軌電壓對(duì)電源系統(tǒng)效率、體積和成本的影響。

推薦閱讀: