【導(dǎo)讀】對(duì)于數(shù)字波束成形相控陣���,要生成本地振蕩器(LO) ,通常會(huì)考慮的實(shí)現(xiàn)方法是向分布于天線陣列中的一系列鎖相環(huán)分配常用基準(zhǔn)頻率�。對(duì)于這些分布式鎖相環(huán),目前文獻(xiàn)中還沒(méi)有充分記錄用于評(píng)估組合相位噪聲性能的方法����。

在分布式系統(tǒng)中,共同噪聲源是相關(guān)的���,而分布式噪聲源如果不相關(guān)��,在 RF 信號(hào)組合時(shí)就會(huì)降低�����。對(duì)于系統(tǒng)中的大部分組件���,這都可以非常直觀地加以評(píng)估��。對(duì)于鎖相環(huán)�����,環(huán)路中的每個(gè)組件都有與之相關(guān)聯(lián)的噪聲傳遞函數(shù),它們的貢獻(xiàn)是控制環(huán)路以及任何頻率轉(zhuǎn)換的函數(shù)�����。這會(huì)在嘗試評(píng)估組合相位噪聲輸出時(shí)增加復(fù)雜性��。本文基于已知的鎖相環(huán)建模方法�,以及對(duì)相關(guān)和不相關(guān)貢獻(xiàn)因素的評(píng)估,提出了跟蹤不同頻率偏移下的分布式PLL貢獻(xiàn)的方法�。

對(duì)于任何無(wú)線電系統(tǒng)��,都需要為接收器和激勵(lì)器精心設(shè)計(jì) LO生成的實(shí)現(xiàn)方法����。隨著數(shù)字波束成形在相控陣天線系統(tǒng)中不斷普及�����,需要在大量分布式接收器和激勵(lì)器中分配 LO 信號(hào)和基準(zhǔn)頻率���,這讓設(shè)計(jì)變得更加復(fù)雜���。

在系統(tǒng)架構(gòu)層面需要權(quán)衡的因素包括,分配所需的LO頻率或分配較低的頻率基準(zhǔn)�,以及在靠近使用點(diǎn)的物理位置產(chǎn)生所需的LO。通過(guò)鎖相環(huán)從本地產(chǎn)生 LO 是一種高度集成的現(xiàn)成選項(xiàng)�。下一個(gè)挑戰(zhàn)是評(píng)估來(lái)自各種分布式組件以及集中式組件的系統(tǒng)級(jí)相位噪聲。

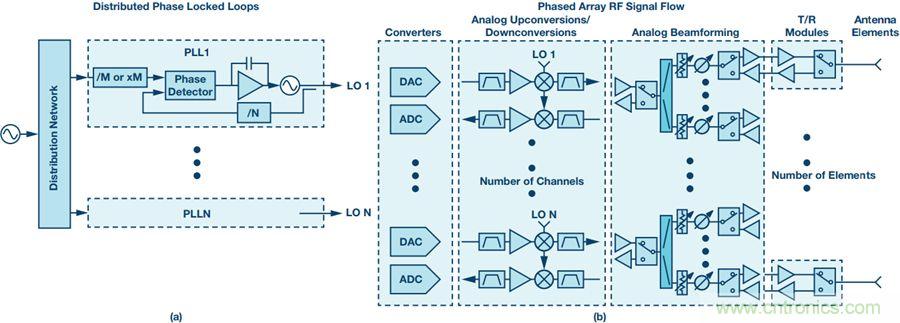

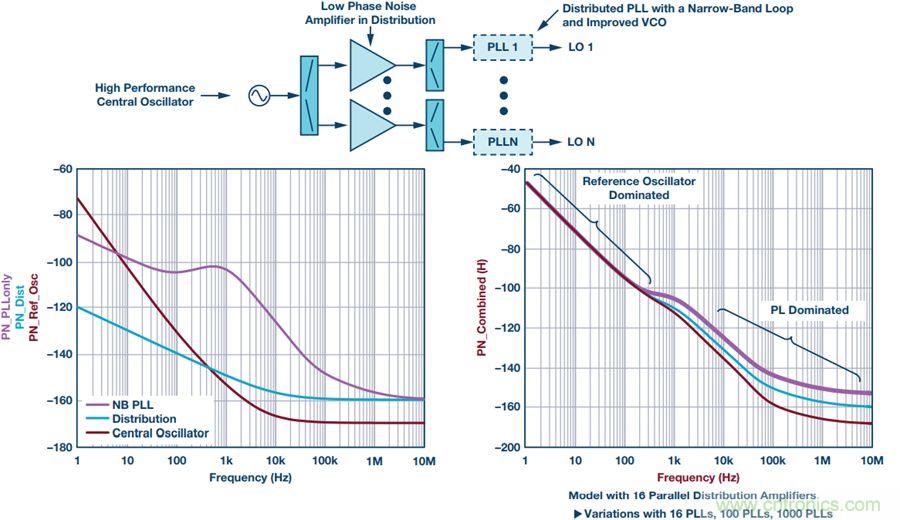

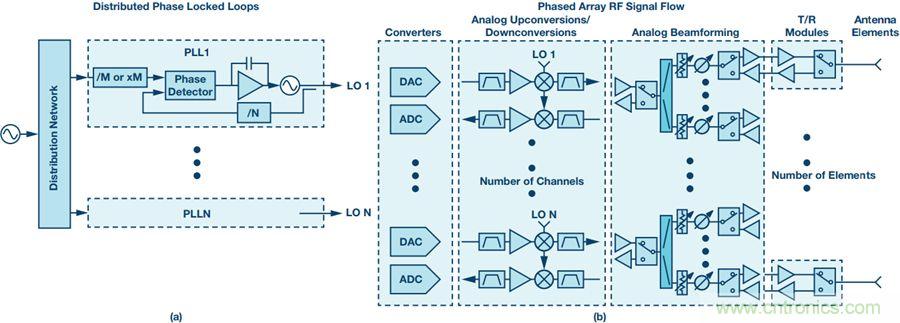

采用分布式鎖相環(huán)的系統(tǒng)如圖1所示�����。常用基準(zhǔn)頻率被分配至多個(gè)鎖相環(huán)����,各產(chǎn)生一個(gè)輸出頻率���。圖1a中的LO輸出被假設(shè)為圖1b的混頻器的LO輸入。

圖1. 分布式鎖相環(huán)系統(tǒng)����。每個(gè)振蕩器都被鎖相到一個(gè)共同的參考振蕩器上。從1到N的LO信號(hào)都應(yīng)用到相控陣中所示的混頻器的LO端口上��。

系統(tǒng)設(shè)計(jì)人員面臨的一個(gè)挑戰(zhàn)是跟蹤分布式系統(tǒng)的噪聲貢獻(xiàn)����、了解相關(guān)和不相關(guān)的噪聲源,并估計(jì)整體的系統(tǒng)噪聲���。在鎖相環(huán)中��,這個(gè)挑戰(zhàn)變得更加嚴(yán)峻��,因?yàn)樵肼晜鬟f函數(shù)都是鎖相環(huán)中的頻率轉(zhuǎn)換和環(huán)路帶寬設(shè)置的函數(shù)。

動(dòng)機(jī):組合鎖相環(huán)測(cè)量示例

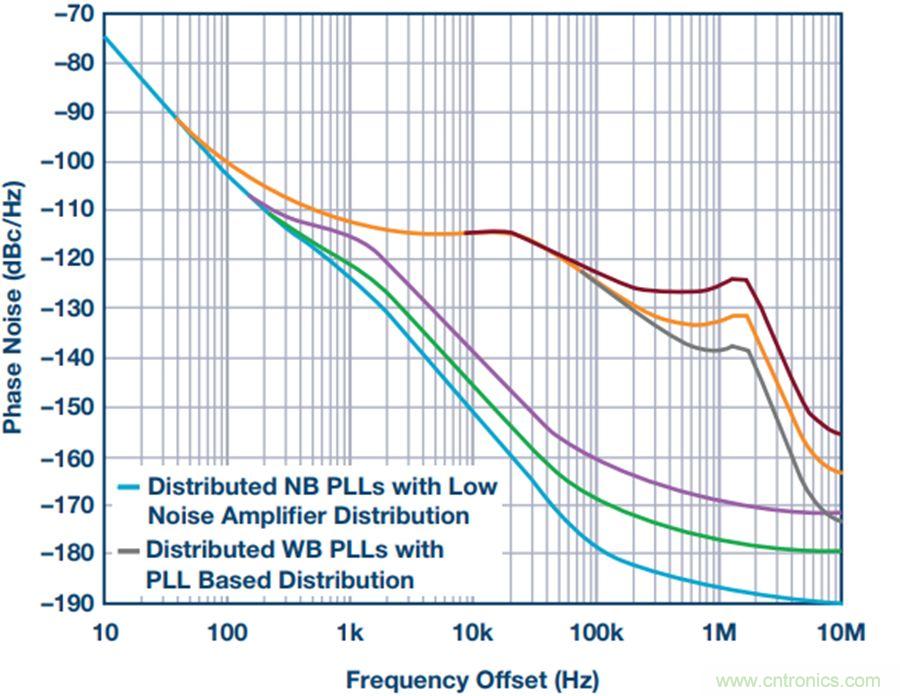

圖2所示為針對(duì)組合鎖相環(huán)的測(cè)量示例��。這些數(shù)據(jù)是通過(guò)組合來(lái)自多個(gè) ADRV9009 收發(fā)器的發(fā)射輸出獲得的��。圖中所示為單個(gè) IC�����、兩個(gè)組合 IC 和 四個(gè)組合 IC 的情況。對(duì)于這個(gè)數(shù)據(jù)集��,在 IC 組合之后��,可以看到明顯的 10logN 改進(jìn)�����。為了達(dá)到這個(gè)結(jié)果��,需要采用一個(gè)低噪聲晶體振蕩器參考源���。下一節(jié)建模的動(dòng)機(jī)是推導(dǎo)出一種方法��,以計(jì)算在具有許多分布式收發(fā)器的大型陣列中�����,更廣泛地說(shuō)是在具有分布式鎖相環(huán)的任何架構(gòu)中����,這種測(cè)量結(jié)果會(huì)如何變化�����。

圖2. 兩個(gè)組合鎖相環(huán)的相位噪聲測(cè)量。

鎖相環(huán)模型

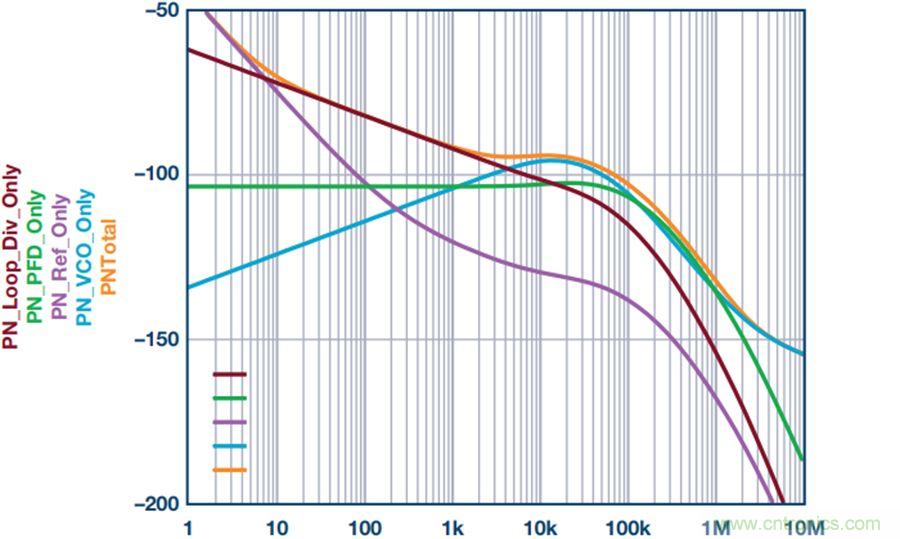

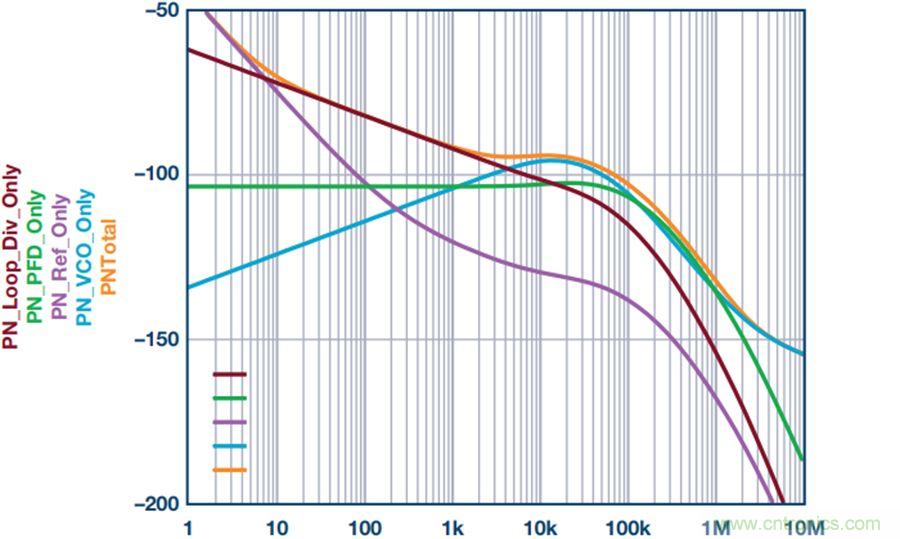

鎖相環(huán)中的噪聲建模已有充分的文檔記錄���。1-5 圖 3 所示為輸出相位噪聲圖���。在這種類(lèi)型的圖中,設(shè)計(jì)師可以快速評(píng)估環(huán)路中每個(gè)組件的噪聲貢獻(xiàn)�����,而這些貢獻(xiàn)因素累計(jì)起來(lái)即可決定整體的噪聲性能�����。模型參數(shù)設(shè)置為代表 圖2 所示的數(shù)據(jù)�,源振蕩器用于估算將大量 IC 組合在一起時(shí)的相位噪聲。

圖3. 典型的鎖相環(huán)相位噪聲分析��,顯示所有組件的噪聲貢獻(xiàn)����?��?傇肼暿撬胸暙I(xiàn)因素的總和�����。

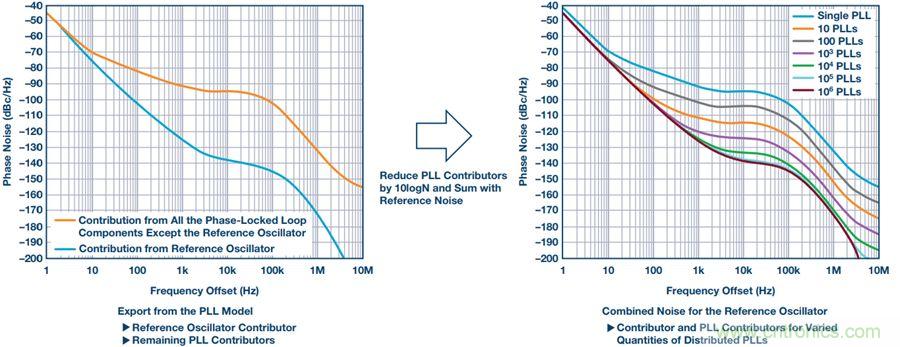

要檢驗(yàn)分布式鎖相環(huán)的效果�����,首先要從PLL模型導(dǎo)出參考貢獻(xiàn)和其余PLL組件的貢獻(xiàn)����。

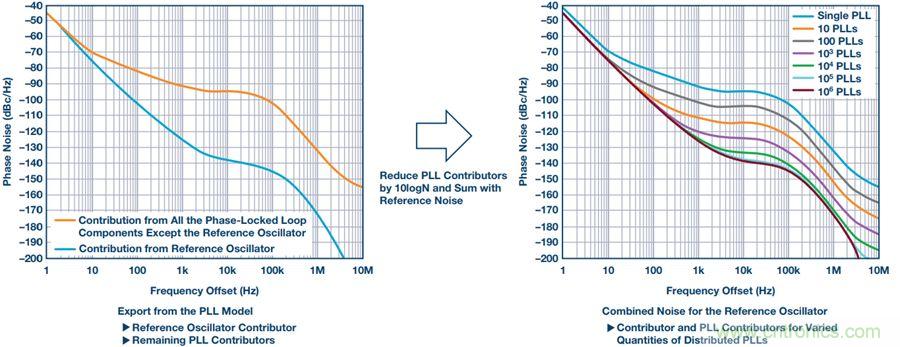

將已知的PLL模型擴(kuò)展為分布式PLL模型

本節(jié)介紹為具有多個(gè)分布式鎖相環(huán)的系統(tǒng)計(jì)算組合相位噪聲的過(guò)程。這種方法的前提是能夠?qū)⒖颊袷幤鞯脑肼曍暙I(xiàn)與VCO和環(huán)路組件的噪聲貢獻(xiàn)分離開(kāi)來(lái)�����。圖4所示為一個(gè)假設(shè)的分布式示例���,一個(gè)參考振蕩器對(duì)應(yīng)多個(gè)PLL��。這個(gè)計(jì)算假設(shè)了一個(gè)無(wú)噪聲分布��,這不切實(shí)際�,但可以用來(lái)說(shuō)明原理。假設(shè)分布式PLL的噪聲貢獻(xiàn)是不相關(guān)的�����,并減少10logN�����,其中N表示分布式PLL的數(shù)量����。隨著通道增加,噪聲在較大偏移頻率下得到改善�����,對(duì)于大型分布系統(tǒng)��,噪聲變得幾乎完全由參考振蕩器主導(dǎo)�����。

圖4. 開(kāi)始采用分布式鎖相環(huán)相位噪聲建模方法:從鎖相環(huán)模型中提取參考振蕩器和鎖相環(huán)中除參考振蕩器外的所有其他組件的相位噪聲貢獻(xiàn)��。作為分布式鎖相環(huán)數(shù)量的函數(shù)�,組合相位噪聲假設(shè)參考噪聲是相關(guān)的����,而分布在多個(gè)PLL之間的噪聲貢獻(xiàn)是不相關(guān)的����。

圖4所示的示例簡(jiǎn)化了對(duì)參考振蕩器分布的假設(shè)��。在真正的系統(tǒng)分析中��,系統(tǒng)設(shè)計(jì)人員還應(yīng)該考慮參考振蕩器分布中的噪聲貢獻(xiàn)�����,它們會(huì)降低總體結(jié)果��。但是��,像這樣的簡(jiǎn)化分析是非常有用的�����,能夠讓人了解架構(gòu)方面的權(quán)衡會(huì)如何影響系統(tǒng)的總體相位噪聲性能�����。接下來(lái)我們來(lái)看看分布系統(tǒng)中相位噪聲的影響。

參考分布中的相位噪聲說(shuō)明

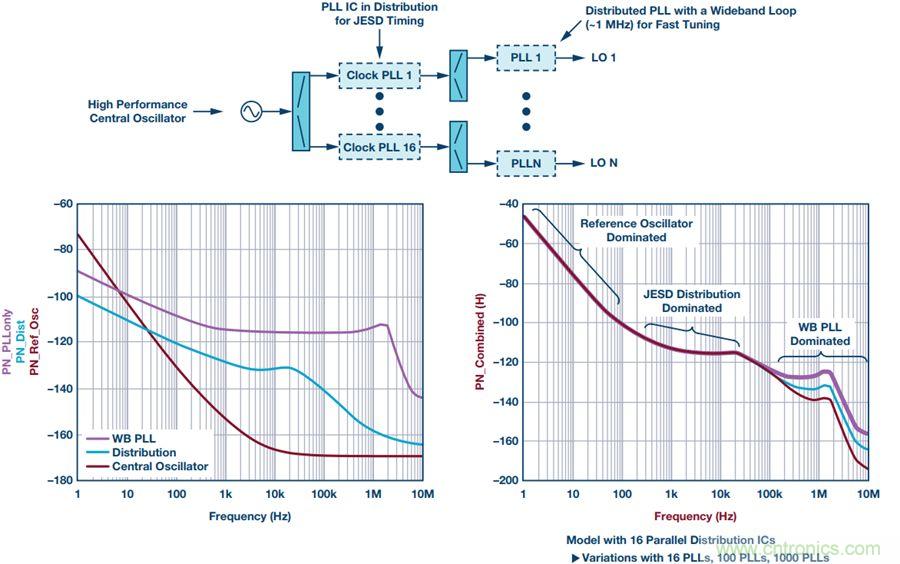

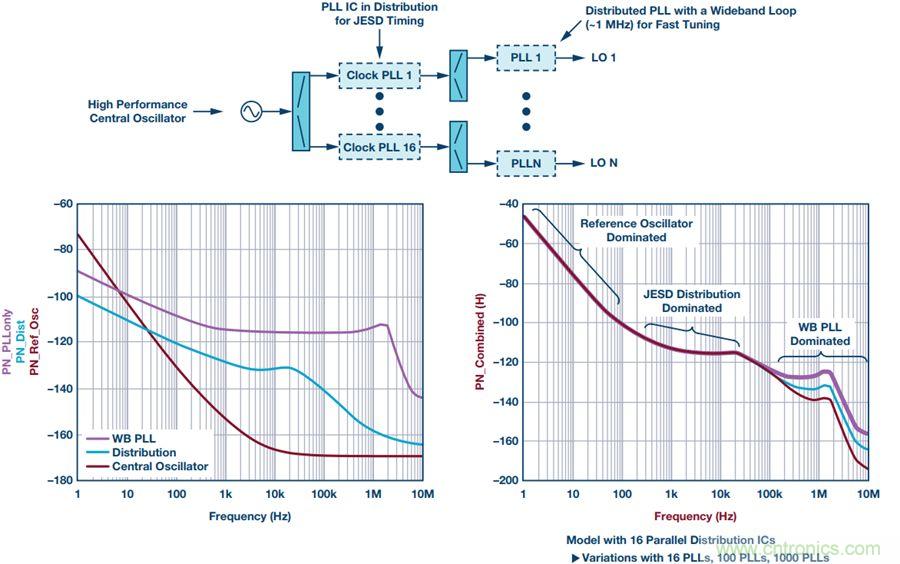

本節(jié)評(píng)估兩個(gè)分布選項(xiàng)示例���?���?紤]的第一種情況如圖5所示���。在這個(gè)示例中�����,選擇了一個(gè)常用于快速調(diào)諧VCO頻率的寬帶PLL��。參考信號(hào)的分布是通過(guò)時(shí)鐘PLL IC實(shí)現(xiàn)的���,這種IC也常用于簡(jiǎn)化數(shù)字?jǐn)?shù)據(jù)鏈路(如JESD接口)的時(shí)序限制。左下角顯示了各個(gè)貢獻(xiàn)因素�����。這些貢獻(xiàn)因素位于器件的頻率��,并未調(diào)整到輸出頻率�。右下角的相位噪聲圖顯示了不同數(shù)量的分布式PLL的系統(tǒng)級(jí)相位噪聲�����。

圖5. 分布中具有PLL IC的分布式寬帶PLL���。

該模型的有些特性值得注意。假設(shè)采用一個(gè)高性能晶體振蕩器�����,標(biāo)稱(chēng)頻率為100 MHz�����,中央振蕩器的單個(gè)貢獻(xiàn)因素反映在可用的較高端晶體振蕩器上���,雖然不一定是最好、最昂貴的可用選擇���。雖然中央振蕩器輸出實(shí)際上會(huì)扇出到有限數(shù)量的分布式PLL�����,但這些PLL會(huì)再次按某個(gè)實(shí)際限值扇出并重復(fù)�,以實(shí)現(xiàn)系統(tǒng)中的完整分布。對(duì)于本例中的分布貢獻(xiàn)�����,假設(shè)有16個(gè)分布組件���,然后假設(shè)它們會(huì)再次扇出��。左下角所示的分布電路的單個(gè)貢獻(xiàn)是不含參考振蕩器貢獻(xiàn)的PLL組件的噪聲�����。本例中的分布假設(shè)與源振蕩器同頻率��,并根據(jù)該函數(shù)可用的典型IC來(lái)選擇噪聲貢獻(xiàn)因素���。

寬帶PLL假設(shè)采用S波段標(biāo)稱(chēng)頻率,設(shè)置采用1 MHz環(huán)路帶寬(盡量與實(shí)際環(huán)路的帶寬一般寬)��,以進(jìn)行快速調(diào)諧��。

值得注意的是��,選擇這些模型是為了代表可能的實(shí)際情況����,且說(shuō)明了陣列中的累積效應(yīng)�����。任何詳細(xì)的設(shè)計(jì)或許都能夠改善特定的PLL噪聲曲線�����,這在預(yù)料之中���,且這種分析方法旨在幫助從工程角度去決定應(yīng)將設(shè)計(jì)資源分配在哪些位置以獲得最佳總體效果���,而不是為了做出相對(duì)于可用組件的確切論斷����。

圖5右下角的圖計(jì)算了LO分布的總組合相位噪聲���。其中應(yīng)用了各個(gè)貢獻(xiàn)因素的PLL噪聲傳遞函數(shù)�����,它們都被調(diào)整至輸出頻率�,也包含PLL環(huán)路帶寬的影響。系統(tǒng)數(shù)量也包括在內(nèi)�����,并且假設(shè)它們是不相關(guān)的����,因此,這個(gè)貢獻(xiàn)減少了10logN��。假設(shè)分布數(shù)量為16����,如前所述,分布貢獻(xiàn)會(huì)減少10log16��。在實(shí)踐中�,隨著分布不斷重復(fù),這種貢獻(xiàn)會(huì)進(jìn)一步減少����。但是,額外的噪聲貢獻(xiàn)不那么顯著�。對(duì)于大型陣列中的扇出分布,噪聲將由第一組有源器件主導(dǎo)。在16組扇出的情況下�����,如果每個(gè)有源器件都是16個(gè)其他有源器件的輸入�,那么在所有器件互不相關(guān)的情況下,16個(gè)器件的額外分布層只會(huì)降低~0.25 dB�����。如果繼續(xù)這種分布��,總體貢獻(xiàn)將更小��。因此��,為了簡(jiǎn)化分析�����,不會(huì)考慮這種影響�����,且分布的噪聲貢獻(xiàn)通過(guò)計(jì)算前16個(gè)并行分布組件得出�。

所得的曲線說(shuō)明了幾種效果���。與單個(gè)PLL模型相似���,近載波噪聲由基準(zhǔn)頻率主導(dǎo)�����,遠(yuǎn)載波噪聲由VCO主導(dǎo)����,且在將不相關(guān)的VCO組合起來(lái)時(shí)���,遠(yuǎn)載波噪聲得到改善�����。這一點(diǎn)相當(dāng)直觀�。不太直觀的是����,模型的值在由分布中的選擇主導(dǎo)的偏移頻率中占較大比重。這一結(jié)果導(dǎo)致考慮具有更低噪聲分布和更窄PLL環(huán)路帶寬的第二個(gè)示例��。

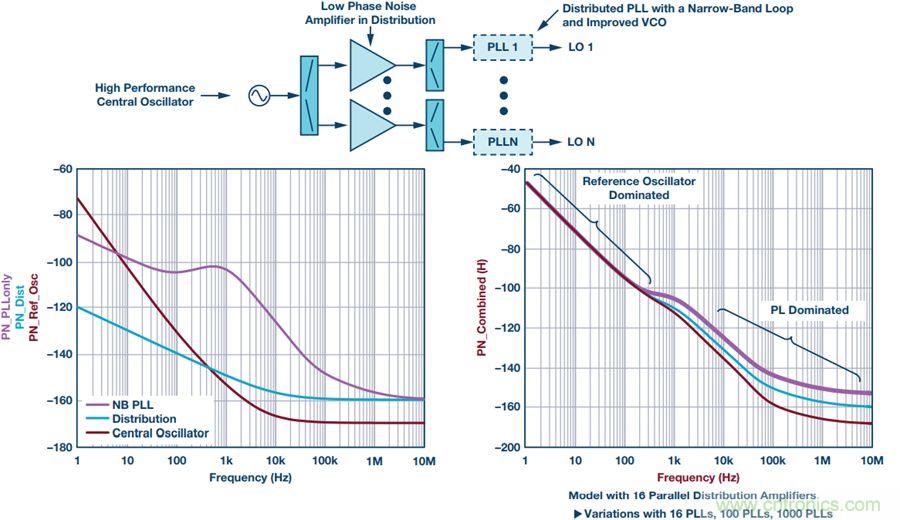

圖6顯示了一種不同的方法。采用相同的低噪聲晶體振蕩器作為參考���。但通過(guò)RF放大器來(lái)分配�,而不是通過(guò)PLL重定時(shí)和重新同步����。選擇固定頻率的分布式PLL。這會(huì)產(chǎn)生兩種效果:采用單個(gè)頻率且調(diào)諧范圍較窄時(shí)��,VCO本質(zhì)上可以更好���,且環(huán)路帶寬可以變得更窄�。左下角的圖顯示了各個(gè)貢獻(xiàn)因素�。中央振蕩器與前一個(gè)例子相同。請(qǐng)注意分布放大器:考慮低相位噪聲放大器時(shí)���,它們的性能不是特別高��,但比起使用PLL LC(如之前的示例)要好得多。VCO更好�����、環(huán)路帶寬更窄時(shí),分布式PLL在更高偏移頻率下會(huì)得到改善�,但在~1 kHz的中間頻率下時(shí),實(shí)際上要比寬帶PLL示例差���。右下角顯示組合結(jié)果:參考振蕩器主導(dǎo)低頻�����,而高于環(huán)路帶寬時(shí)����,性能會(huì)由分布式PLL主導(dǎo)�����,且隨著分布式PLL的陣列尺寸和數(shù)量增加而提高��。

圖6. 分布式窄帶PLL�����,分布中具備放大器��。

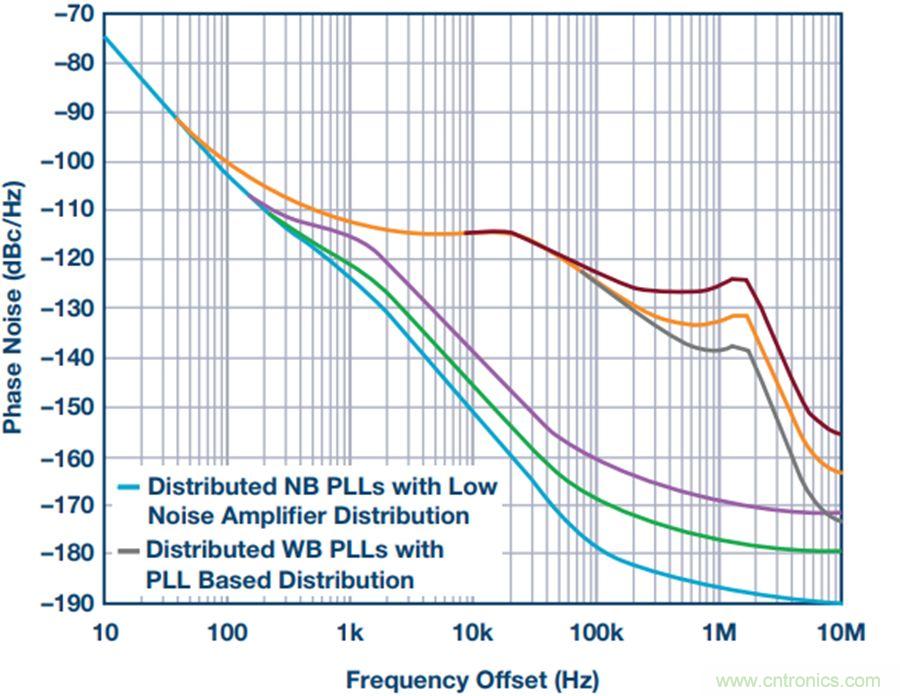

圖7顯示這兩個(gè)示例之間的比較����。注意~2 kHz到5 kHz偏移頻率范圍內(nèi)的大范圍差異�����。

圖7. 圖5和圖6之間的比較�����,顯示了基于所選的分布和架構(gòu)的廣泛系統(tǒng)級(jí)性能范圍�����。

分布式PLL陣列級(jí)考慮因素

基于對(duì)總體系統(tǒng)相位噪聲性能的加權(quán)貢獻(xiàn)的理解��,可以得出幾個(gè)與相控陣或多通道RF系統(tǒng)架構(gòu)相關(guān)的結(jié)論��。

PLL帶寬

針對(duì)相位噪聲優(yōu)化的傳統(tǒng)鎖相環(huán)設(shè)計(jì)將環(huán)路帶寬設(shè)置為偏移頻率�����,以最小化總體相位噪聲曲線�����。此時(shí)的頻率一般是參考振蕩器相位噪聲按輸出頻率標(biāo)準(zhǔn)化后與VCO相位噪聲相交的頻率��。對(duì)于具有多個(gè)鎖相環(huán)的分布式系統(tǒng)��,這可能不是最佳環(huán)路帶寬��。分布式組件的數(shù)量也需要考慮�。

要在采用分布式鎖相環(huán)實(shí)現(xiàn)的系統(tǒng)中獲得最佳LO噪聲�,需要采用一個(gè)較窄的環(huán)路帶寬來(lái)最小化參考振蕩器的相關(guān)噪聲貢獻(xiàn)。

對(duì)于需要快速調(diào)優(yōu)PLL的系統(tǒng)��,通常會(huì)擴(kuò)大環(huán)路帶寬來(lái)優(yōu)化速度����。遺憾的是,這種優(yōu)化分布式相位噪聲貢獻(xiàn)的思路本身就是背道而馳的����。克服這一問(wèn)題的選擇之一是在寬帶環(huán)路之前設(shè)置分布式窄帶清理環(huán)路�,以降低參考噪聲和分布噪聲相關(guān)位置的偏移頻率。

大型陣列

對(duì)于使用數(shù)千個(gè)通道的系統(tǒng)����,如果分布式組件的貢獻(xiàn)之間保持互不相關(guān),則系統(tǒng)能夠獲得大幅改進(jìn)��。主要考慮的問(wèn)題可能?chē)@參考振蕩器的選擇展開(kāi),以及面向分布式接收器和激勵(lì)器維持低噪聲分布系統(tǒng)�����。

直接采樣系統(tǒng)

隨著速度和RF輸入帶寬持續(xù)提升的GSPS轉(zhuǎn)換器的不斷普及��,直接采樣系統(tǒng)正逐漸在微波頻率實(shí)現(xiàn)�。這導(dǎo)致出現(xiàn)一種有趣的取舍現(xiàn)象。數(shù)據(jù)轉(zhuǎn)換器只需要一個(gè)時(shí)鐘頻率��,RF調(diào)諧完全在數(shù)字域中完成�����。通過(guò)限制調(diào)諧范圍����,可以構(gòu)建具備相位噪聲性能更高的VCO。這也使得創(chuàng)建數(shù)據(jù)轉(zhuǎn)換器時(shí)鐘的PLL的環(huán)路帶寬降低���。更低的環(huán)路帶寬會(huì)將參考振蕩器的噪聲傳遞函數(shù)降至更低的偏移頻率��,從而減少它在系統(tǒng)中的貢獻(xiàn)���。這一點(diǎn)�,再加上改進(jìn)過(guò)的VCO�,在某些情況下可能給分布式系統(tǒng)帶來(lái)好處,即使單通道比較結(jié)果似乎更青睞替代架構(gòu)�。

組件選項(xiàng)

根據(jù)系統(tǒng)架構(gòu)中所需的選擇��,設(shè)計(jì)人員擁有大量可用的組件選項(xiàng)�����。2018年度RF�����、微波和毫米波產(chǎn)品選型指南更新版現(xiàn)已發(fā)布�����,需要的親可點(diǎn)擊“閱讀原文”免費(fèi)獲取��。

集成 VCO/PLL 選項(xiàng)包括 ADF4371/ADF4372����。它們提供的輸出頻率分別高達(dá)32 GHz和16 GHz,采用–234 dBc/Hz的先進(jìn)PLL相位噪聲FOM����。 ADF5610 提供高達(dá)15 GHz的輸出����。 ADF5355/ADF5356 的輸出可達(dá)13.6 GHz��,ADF4356的輸出可達(dá)6.8 GHz�。

對(duì)于單獨(dú)的PLL和VCO配置, ADF41513 的工作頻率可達(dá)26 GHz��,且配有一個(gè)先進(jìn)的鎖相環(huán)相位噪聲FOM����,其相位噪聲FOM為-234dBc/Hz。有時(shí)���,在選擇PLL IC時(shí)要考慮的一個(gè)問(wèn)題是在盡可能高的頻率上操作鑒相器���,從倍增20logN到輸出頻率,最小化環(huán)路中的噪聲�。 HMC440, HMC4069, HMC698 和 HMC699 采用的PFD的工作頻率高達(dá)1.3 GHz。對(duì)于VCO����,2018年選型指南列出了幾十個(gè)VCO選項(xiàng)�,范圍從2 GHz到26 GHz不等����。

對(duì)于直接采樣選項(xiàng),ADC 和 DAC 均已發(fā)布���。產(chǎn)品支持在L頻段和S頻段直接采樣。ADC具有更高的輸入頻率帶寬�����,支持C頻段直接采樣��。 AD9208 是一個(gè)雙通道3 GSPS ADC��,輸入頻率為9 Ghz���,支持在上Nyquist區(qū)采樣��。AD9213是一個(gè)單通道10 GSPS ADC��,支持具有較大瞬時(shí)帶寬的接收器�����。對(duì)于DAC, AD917x系列采用雙通道12 GSPS DAC�,AD916x系列采用單通道12 GSPS DAC,經(jīng)過(guò)優(yōu)化之后可實(shí)現(xiàn)更低的殘留相位噪聲和更好的SFDR��。兩個(gè)系列都支持L頻段和S頻段波形生成�����。

PS.本節(jié)僅提供入門(mén)指南�。

結(jié)語(yǔ)

本文介紹了為采用分布式鎖相環(huán)的系統(tǒng)評(píng)估相位噪聲的方法。該方法的前提是:每個(gè)組件都可以通過(guò)其各自的噪聲����、組件與系統(tǒng)輸出之間的噪聲傳遞函數(shù)、使用的數(shù)量以及器件之間的任何相關(guān)性來(lái)進(jìn)行跟蹤����。所示的示例并不意在對(duì)可用的組件或架構(gòu)功能進(jìn)行論斷。它們旨在說(shuō)明一種方法�����,以幫助設(shè)計(jì)人員在數(shù)字波束成形相控陣中�,對(duì)LO中的陣列級(jí)相位噪聲貢獻(xiàn)因素以及為分布式波形發(fā)生器和接收器提供服務(wù)的時(shí)鐘分布網(wǎng)絡(luò)進(jìn)行有根據(jù)的評(píng)估���。

推薦閱讀: