【導讀】集成無源器件在我們的行業(yè)中并不是什么新事物——它們由來已久且眾所周知。實際上,ADI公司過去曾為市場生產(chǎn)過這類元件。當芯片組將獨立的分立無源器件或者是集成無源網(wǎng)絡作為其一部分包含在內(nèi)時,需要對走線寄生效應、器件兼容性和電路板組裝等考慮因素進行仔細的設計管理。雖然集成無源器件繼續(xù)在業(yè)界占據(jù)重要地位,但只有當它們被集成到系統(tǒng)級封裝應用中時才能實現(xiàn)其最重要的價值。

幾年前,ADI開始推出新的集成無源技術計劃 (iPassives™)。ADI旨在通過這項計劃提供二極管、電阻、電感和電容等無源元件,從而能夠更廣泛地涵蓋信號鏈設計,同時克服現(xiàn)有采用無源元件方法的局限性和復雜性。ADI的客戶群對具有高效空間尺寸的更完整解決方案的需求,也推動了這項計劃的發(fā)展。從設計人員的角度來看,iPassives可以被視為一種靈活的設計工具,能夠在極短的開發(fā)周期內(nèi)設計出具有同類最佳性能和魯棒性的系統(tǒng)解決方案。ADI擁有許多信號調理IC,我們擁有的獨特硅制造工藝使這些IC能夠實現(xiàn)卓越的性能。ADI可以充分利用其現(xiàn)有產(chǎn)品的多樣性來生產(chǎn)具有卓越性能特征的即插即用系統(tǒng),而無需開發(fā)高度復雜的集成流程。在高度可定制的網(wǎng)絡中將集成無源技術與所有這些現(xiàn)有技術緊密結合,并利用系統(tǒng)級封裝技術進行封裝,從而可創(chuàng)建完全經(jīng)過認證、測試和表征的 Module®器件。以前采用板級解決方案的系統(tǒng)現(xiàn)在可以簡化為單個器件。從我們的客戶角度來看,他們現(xiàn)在可以獲得完整的解決方案,具有出色的開箱即用性能,可縮短開發(fā)周期并節(jié)約成本,而且所有這些都在非常緊湊的封裝內(nèi)實現(xiàn)。

無源技術

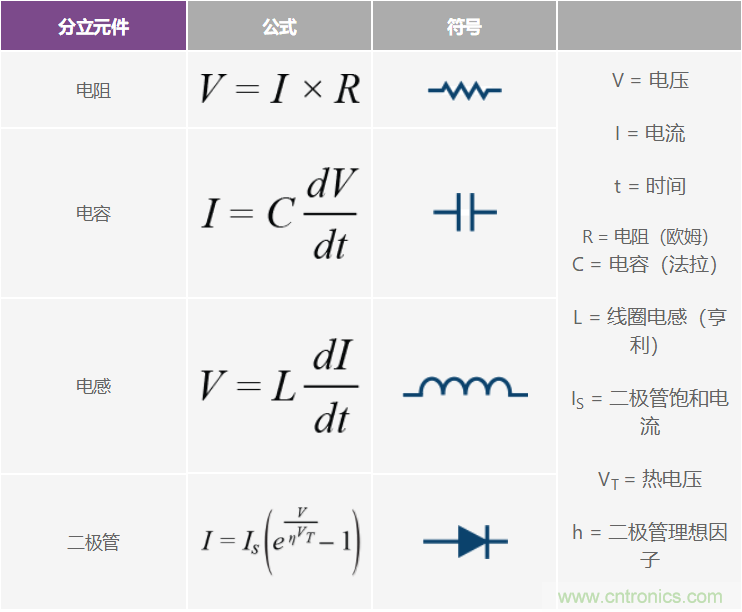

現(xiàn)在,我們來簡要回顧一下基礎知識,回想一下什么是無源元件。無源元件是無需電源供電的器件,它們的電流和電壓之間的關系相對簡單。這些元件包括電阻、電容、電感、變壓器(即有效耦合電感)和二極管。有時電流-電壓之間的關系非常簡單,就像電阻中電流隨電壓線性變化一樣。對于二極管來說,電流和電壓之間也存在直接關系,只是這種關系是指數(shù)關系。在電感和電容中,該關系是電流對電壓的瞬態(tài)依賴性。表1所示為四種基本無源元件定義這些關系的公式:

表1. 主要無源元件的基本公式

無源器件既可以單獨使用,也可以串聯(lián)或并聯(lián),是模擬信號處理(RLC用于放大、衰減、耦合、調諧和濾波)、數(shù)字信號處理(上拉電阻、下拉電阻和阻抗匹配電阻)、EMI抑制(LC噪聲抑制)和電源管理(R用于電流檢測和限制,LC用于能量累積)的重要組成部分。

分立元件的局限性

過去,無源元件是分立的,這意味著它們是分別制造的,并且在電路中通過印刷電路板 (PCB) 上的導線或電源軌相連。隨著時間的推移,它們沿著三條路徑發(fā)展演變:更小的尺寸、更低的成本和更高的性能。這些發(fā)展現(xiàn)在已經(jīng)很成熟并經(jīng)過了優(yōu)化,但是占位尺寸和高度尺寸意味著分立無源元件總是限制了縮小整體解決方案的面積和體積的努力成效。無源器件通常在一個應用中占物料清單的80%以上,占線路板面積約60%,占整個元件支出約20%。這些因素綜合在一起帶來了非常復雜的庫存控制和存儲挑戰(zhàn)。

就其本質而言,分立器件是單獨處理的元件。盡管可能有一些方法可以確保從某些工藝批次中選擇元件,但每個元件仍然具有高度的獨特性。然而,當需要非常匹配的元件時,這是一個顯著的缺點。對于需要匹配的設備來說,元件之間的獨特性和差異性會導致誤差,從而降低時間零點的電路性能。此外,在電路的工作溫度范圍內(nèi)及使用壽命期間,這種性能下降總是越來越糟糕。

分立無源器件的另一個缺點是各個元件的組裝和布線非常耗時,并且還占用很大的空間。這些元件使用焊接工藝連接,一般是通過通孔或表貼封裝技術(SMT)組裝。通孔是一種比較老的組裝技術,它將帶引線的器件插入PCB的孔中,任何多余的引線長度都將被折彎并切除,并通過波峰焊將器件的引線連接至PCB互連電源軌。表貼封裝幫助實現(xiàn)了更小的無源元件。在這種情況下,在PCB上蝕刻貼裝連接圖案,將焊錫膏覆蓋在圖案上,接著使用貼片機來定位放置SMT元件。然后,PCB經(jīng)過回流焊工藝(其間焊錫膏液化并建立電氣連接),并在冷卻時,焊錫膏凝固并將SMT元件機械連接到PCB上。這兩種組裝技術的主要問題是,焊接過程可能非常不可靠,在缺陷目標是每百萬分之幾的行業(yè)中,這一點越來越令人擔憂。在確保焊點可靠性方面有幾個因素非常重要:焊錫膏的實際成分(現(xiàn)在基本上都是無鉛的,因此可靠性降低)、回流焊工藝中的機械穩(wěn)定性(機械振動可使焊點干燥)、焊錫膏的純度(任何污染物都會對焊點的可靠性產(chǎn)生負面影響),以及回流焊工藝中的時間與溫度。焊錫膏加熱的速度如何、實際溫度和溫度的均勻性怎樣以及焊錫膏加熱的時間都非常關鍵。其中的任何變化都可能導致連接焊盤或通孔的損壞,或者也可能引起器件上的機械應力,隨著時間的推移而導致故障。

在PCB上采用無源元件的另一個局限是,由于它們板上分布在各處,走線需要很長。這可能會引入未計入的寄生參數(shù),從而使性能和結果的可重復性受限。通常,PCB走線具有大約1 nH/mm自感的長度和電容,取決于線寬和與附近走線的距離。PCB走線的容差導致了寄生參數(shù)的變異,所以不僅帶來寄生效應的破壞性,而且它們還是不可預測的。在PCB板上縮小容差會增加成本。

無源器件還提供了許多與外界的潛在接觸點,這些接觸點經(jīng)手動處理或機器處理可能會引起ESD事件。同樣,這對整體可靠性和魯棒性會造成不利影響和風險。

集成無源器件的優(yōu)勢

在深入探討集成無源器件相比分立無源器件的優(yōu)勢之前,我們首先概述一下集成無源器件的起源。集成電路現(xiàn)在包含了許多晶體管(實際上是數(shù)百萬個),它們由精細的金屬互相連接在一起。針對模擬類的應用,業(yè)界還開發(fā)了特殊的工藝,如DAC和ADC中除了晶體管,還包含電阻和電容等無源元件。為了實現(xiàn)這些精密的模擬應用所需的性能,已經(jīng)開發(fā)出質量非常高的無源元件。用來構建集成無源器件的正是這些高質量的無源元件。正如集成電路中包含許多晶體管一樣,集成無源器件可以在一個非常小的封裝內(nèi)包含許多高質量的無源元件。與集成電路一樣,集成無源器件在大面積襯底(晶圓)上制造,同時生成多個無源網(wǎng)絡。

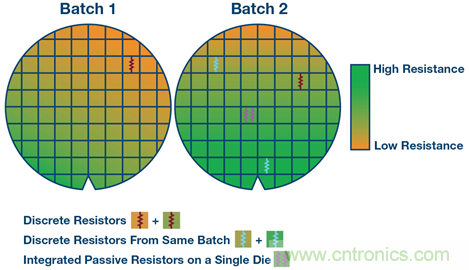

與分立無源元件相比,集成無源器件最引人注目的優(yōu)勢之一是可以實現(xiàn)精確匹配。在制造集成無源網(wǎng)絡時,網(wǎng)絡內(nèi)的所有元件都是在相同條件下同時制造的,具有相同的材料,而且由于網(wǎng)絡緊湊,基本上是在同一位置。采用這種方式制造的無源元件比分立無源元件更可能具有出色的匹配。為了說明這一點,我們假設有一個應用需要兩個匹配的電阻。這些電阻在圓形襯底(如硅晶圓)上制造,如圖1所示。由于細微的工藝差異,如電阻薄膜的厚度、薄膜的化學性質、接觸電阻等,因此在同一個批次內(nèi)將存在一定的阻值差異,而在多個批次里差異值更大。在圖1所示的例子中,深綠色表示電阻在容差范圍的高位值端,黃色表示電阻在容差范圍的低位值端。

對于標準的分立器件來說,兩個電阻中的任意一個都可能來自不同的制造批次,如圖中用紅色表示的兩個單獨的電阻。這兩個分立電阻之間可觀察到的容差范圍可能是整個工藝的容差范圍,因此匹配較差。對于有特殊的訂購限制而言,有可能從同一個批次中選擇這兩個分立電阻,如圖中用藍色標出的兩個單獨的電阻。這兩個電阻之間可觀察到的容差只會是在同一個批次內(nèi)的容差范圍。雖然這兩個電阻之間的匹配將優(yōu)于隨機分立器件的情況,但仍有可能出現(xiàn)某種程度的不匹配。最后,對于集成無源器件,兩個電阻來自同一個芯片,如圖1黑色所示。這兩個電阻之間唯一可觀察到的容差是在同一個管芯內(nèi)的容差范圍。因此,這兩個電阻之間的匹配將非常出色。此外,使用交叉四邊形布局的其他技術和其他方法可以進一步嚴格限制兩個電阻之間的擴散,使元件的匹配達到最佳值。集成無源元件之間的匹配不僅在時間零點比分立無源元件要好得多,而且由于其制造已經(jīng)很好地耦合,因此在整個溫度、機械應力和使用壽命范圍內(nèi)都可保持更好的匹配記錄。

圖1. 分立電阻與無源電阻的匹配比較。

集成無源器件中的各個元件緊密地放置在一起(實際上在微米范圍內(nèi)),因此,互連寄生參數(shù)(如布線電阻和電感)可以保持在極低的水平。在PCB上,由于走線容差和元件放置容差,互連寄生參數(shù)可能會發(fā)生變化。由于制造工藝中采用微影工藝,因此使用集成無源器件的互連容差和元件放置容差都很小。在集成無源器件中,不僅寄生參數(shù)非常小,而且這些為數(shù)不多的參數(shù)還是可預測的,因此可靠性很高。

通過集成無源器件實現(xiàn)無源網(wǎng)絡的小型化,為電路板直接帶來小尺寸的優(yōu)勢。這直接使電路板成本降低,并允許在更小的占位空間上實現(xiàn)更多功能和更高性能。使用集成無源器件時,構建多通道系統(tǒng)變得更加實際可行。

集成無源器件的另一個顯著優(yōu)勢是其整個布線網(wǎng)絡周圍的魯棒性。集成無源器件本質上是在一個完整的單元里一起鍛造,用玻璃密封,然后進一步由牢固的塑料封裝進行保護,而不需要大量的焊接連接。在集成無源網(wǎng)絡中,不存在焊點干燥、腐蝕或元件錯位的問題。

集成無源網(wǎng)絡密封性能出色帶來的另一個優(yōu)勢是,系統(tǒng)中暴露節(jié)點的數(shù)量大大減少。因此,系統(tǒng)因意外短路或靜電放電 (ESD) 事件損壞的可能性顯著降低。

維護和控制任何電路板組裝的元件庫存都是一項非常復雜的任務。集成無源器件在一個器件內(nèi)包含多個無源元件,大大減輕了客戶的物料清單負擔,從而降低擁有成本??蛻艨梢垣@得經(jīng)過完全測試和充分驗證的集成無源網(wǎng)絡。這意味著,最終線路板構建的產(chǎn)量得到提高,這不僅可以進一步節(jié)省成本,還可以提高供應鏈的可預測性。

使用ADI的集成無源器件(iPassives)

如前所述,高質量的無源器件一直是ADI多年來眾多產(chǎn)品所實現(xiàn)的電路性能的核心。在此期間,無源器件的范圍不斷擴大并且質量不斷提高,集成無源器件產(chǎn)品組合現(xiàn)在包含大量元件。集成無源器件采用模塊化工藝,這意味著只有在需要特定元件時才需要執(zhí)行生產(chǎn)某種類型無源器件所需的工藝步驟。iPassives網(wǎng)絡的構建基本上只需要必需的工藝復雜性,不多也不少。如圖2所示,有許多無源構建塊可供選擇,構建一個集成無源網(wǎng)絡就像將所需元件拼裝在一起一樣簡單。

圖2. iPassives構建塊。

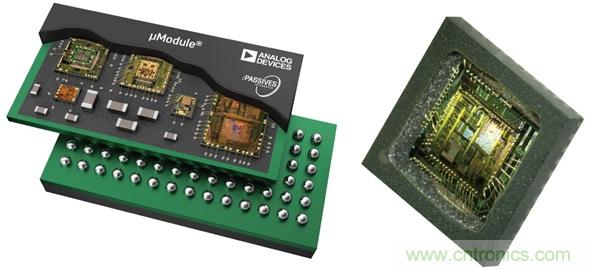

如本文前面所述,集成無源器件與分立無源器件相比具有許多優(yōu)勢。ADI將它們用于 Module器件中,進一步加強了這些優(yōu)勢。這些模塊利用了各種集成電路的功能。這些電路通過量身定制的工藝進行制造,所提供的增強性能是無法通過其他任何單一工藝實現(xiàn)的。ADI正在使用iPassives將這些集成電路連接在一起,由此在單個器件內(nèi)構建完整的精密信號鏈。圖3中的兩個 Module器件示例包括數(shù)據(jù)轉換器、放大器和其他元件,通過采用集成無源器件構建的無源增益和濾波網(wǎng)絡將它們結合在一起。

圖3. 使用iPassives的μModule產(chǎn)品示例。

ADI生產(chǎn)高度可定制的精密信號調理系統(tǒng)。采用來自大量經(jīng)現(xiàn)場驗證的IC產(chǎn)品組合的可重復使用的方法,并將其與iPassives的多功能性相結合,從而使開發(fā)周期時間和成本都顯著下降。這一決定為客戶提供了巨大的優(yōu)勢,使客戶可以自行利用最先進的性能更快、更高效地進入市場。

結論

乍一看,使用集成無源器件可能只會比其他更成熟的方法顯得略微有利。然而,實際優(yōu)勢更為顯著,ADI采用iPassives不僅重新定義了可以實現(xiàn)的功能,還重新定義了速度、成本和設計尺寸,使之對客戶更為有利。

推薦閱讀: