【導(dǎo)讀】陀螺儀是一種能夠精確地確定運動物體方位的儀器,它是現(xiàn)代航空、航海、航天和國防工業(yè)中廣泛使用的一種慣性導(dǎo)航儀器,它的發(fā)展對一個國家的工業(yè),國防和其他高科技的發(fā)展具有十分重要的戰(zhàn)略意義。

近年來隨著MEMS(微機電系統(tǒng))技術(shù)的發(fā)展,MEMS陀螺儀的研究與發(fā)展受到了廣泛的重視。MEMS陀螺儀具有體積少、重量輕、可靠性好、易于系統(tǒng)集成等優(yōu)點,應(yīng)用范圍廣闊。但是目前MEMS陀螺儀的精度還不是很高,要想大范圍應(yīng)用必須對MEMS陀螺儀的信號進行處理。

本文選用TI公司的TMS320VC33作為MEMS陀螺儀信號處理平臺的核心芯片,同時引入DSP/BIOS實時操作系統(tǒng)提供的多任務(wù)處理機制,在對陀螺儀信號進行數(shù)據(jù)采集的間隙同時對先采集來的信號數(shù)據(jù)進行處理和傳輸,確保數(shù)據(jù)采集和處理的實時性,大大提高了信號處理平臺的工作效率,在高速實時數(shù)據(jù)采集和處理領(lǐng)域具有一定的應(yīng)用價值。

1 MEMS陀螺儀信號處理平臺的硬件結(jié)構(gòu)

1.1 信號處理平臺的硬件結(jié)構(gòu)及工作原理

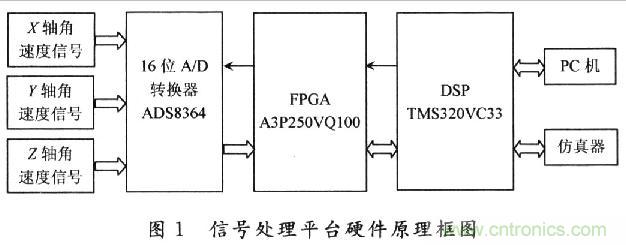

MEMS陀螺儀信號的處理平臺的硬件系統(tǒng)應(yīng)該包括以下幾個部分:DSP模塊,數(shù)據(jù)采集模塊,上位機通信模塊和JTAG調(diào)試接口模塊。

數(shù)據(jù)采集模塊由兩部分組成:6路16位模/數(shù)轉(zhuǎn)換器ADS8364和同步時序控制器FPGA(A3P250VQ100)。FPGA(A3P250VQ100)一方面是控制各個單元時序,另一方面是為了對A/D采集來的陀螺信號進行預(yù)處理。

模/數(shù)轉(zhuǎn)換器ADS8364通過FPGA與DSPVC33相連,采集三軸陀螺信號。

DSP主要完成對陀螺信號的降噪運算。陀螺信號經(jīng)DSP處理后再由SCI接口傳送到上位機。

系統(tǒng)設(shè)計的原理框圖如圖1所示。

在圖1中三路陀螺模擬信號經(jīng)過各自的信號調(diào)理、抗混迭濾波后進入多通道A/D轉(zhuǎn)換器,在FPGA的控制下選擇一路信號進行轉(zhuǎn)換,轉(zhuǎn)換結(jié)果送入FPGA片上FIFO緩存,由DSP讀取數(shù)據(jù)并進行數(shù)字信號處理。同時FPGA對A/D轉(zhuǎn)換器傳過來的信號進行預(yù)處理,再送到DSP進行信號降噪處理,保證了MEMS陀螺信號處理系統(tǒng)處理的實時性。然后DSP把處理后的結(jié)果送至上位機和經(jīng)過串口輸出,完成數(shù)字輸出和模擬輸出,滿足不同的應(yīng)用要求。

1.2 信號處理平臺A/D電路設(shè)計

在整個MEME陀螺信號處理平臺中,A/D轉(zhuǎn)換器是整個系統(tǒng)數(shù)據(jù)采集部分關(guān)鍵核心器件,信號處理系統(tǒng)中選用了美國德州儀器(TI)公司的ADS8364作為MEMS陀螺信號處理平臺的A/D轉(zhuǎn)換器。ADS8364是TI公司推出的高速、低功耗、6通道16位A/D轉(zhuǎn)換芯片,共有64個引腳。其時鐘信號由外部提供,最高頻率為5 MHz,對應(yīng)的采樣頻率是250 kHz。數(shù)字電源供電電壓為3~5 V,即可以與3.3 V供電的微控制器接口,也可以與5 V供電的微控制器接口。所以ADS8364非常適合應(yīng)用在精度要求較高,結(jié)構(gòu)簡單的嵌入式信號處理系統(tǒng)中。

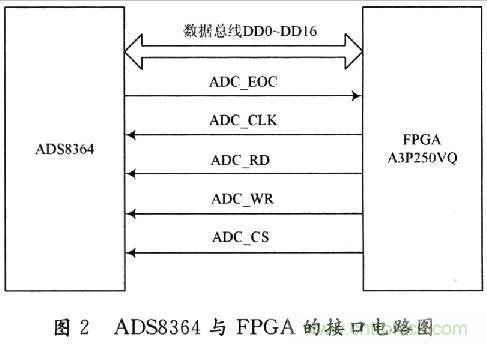

ADS8364的時鐘信號由外部提供,這里由FPGA提供時鐘信號,主要是考慮到FPGA可以靈活地改變時鐘頻率,進而改變系統(tǒng)的采樣頻率。A/D轉(zhuǎn)換完成后產(chǎn)生轉(zhuǎn)換結(jié)束信號EOC。將ADS8364的BYTE引腳接低電平,使轉(zhuǎn)換結(jié)果以16位的方式輸出。地址/模式信號(A0,A1,A2)決定ADS8364的數(shù)據(jù)讀取方式,可以選擇的方式包括單通道、周期或FIFO模式。將ADD引腳置為高電平,使得讀出的數(shù)據(jù)中包含轉(zhuǎn)換通道信息??紤]到數(shù)據(jù)采集處理系統(tǒng)的采樣頻率一般較高,如果用DSP直接控制ADS8364的訪問,將占用DSP較多的資源,同時對DSP的實時性要求也較高。因此在本系統(tǒng)設(shè)計中,用FPGA實現(xiàn)ADS8364的接口控制電路,并將轉(zhuǎn)換結(jié)果存儲在FPGA中,用DSP實現(xiàn)FPGA芯片的輸出接口。圖2為ADS8364與FPGA的接口電路設(shè)計圖。

1.3 DSP的串行通信接口設(shè)計

TMS320VC33 DSP中的串口是一種同步串行接口,串行通信接口(SCI)是采用雙線通信的異步串行通信接口,即通常所說的UART口,VC33內(nèi)部帶有串行通信模塊,該串口支持16級接收和發(fā)送FIFO,可以與PC和其他異步通信外設(shè)進行數(shù)字通信,在信號處理平臺系統(tǒng)中采用RS 232通信方式將數(shù)據(jù)發(fā)給上位機,與TMS320VC33接口的外設(shè)選用MAX3232。

2 MEMS陀螺儀信號處理平臺系統(tǒng)任務(wù)分析

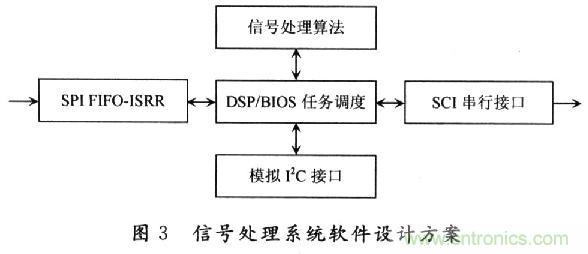

MEMS信號處理系統(tǒng)劃分為三個獨立的任務(wù):數(shù)據(jù)采集任務(wù)、陀螺信號處理任務(wù)和上位機通信任務(wù)。各個任務(wù)之間通過DSP/BIOS的旗語信號量進行同步和協(xié)調(diào)。

數(shù)據(jù)采集任務(wù)是負責(zé)對MEMS陀螺的信號進行采集。該任務(wù)是系統(tǒng)的關(guān)鍵部分,優(yōu)先級最高,執(zhí)行時間比其他任務(wù)短,因此選用DSP/BIOs的硬件中斷模塊(HWI)。硬件中斷模塊(HWI)具有嚴格的實時性和高優(yōu)先級,一旦SPIFIFO接收寄存器被外部ADC寫滿,立即產(chǎn)生相應(yīng)的中斷,CPU立即掛起當(dāng)前的任務(wù),調(diào)用相應(yīng)的中斷服務(wù)程序數(shù)據(jù)采集任務(wù),將FIFO緩沖區(qū)內(nèi)的采樣值讀入接收數(shù)據(jù)緩沖區(qū),啟動后續(xù)采樣。這時中斷服務(wù)程序退出,CPU的控制權(quán)返還給先前的任務(wù)。

陀螺信號處理任務(wù)負責(zé)對采集到的數(shù)字量信號進行小波除噪和溫度補償?shù)人惴ㄌ幚?。在設(shè)計時引入了DSP/BIOS的另一種線程類型TSK來實現(xiàn)。任務(wù)是獨立使用的CPU進程,真正體現(xiàn)了多線程的思想,支持阻塞和優(yōu)先級搶斷。

TSK共有15個優(yōu)先級,每個任務(wù)均有自己獨立的堆棧,響應(yīng)延時比較長,適合對實時性要求不是很高的進程。TSK對象的優(yōu)先級低于硬件中斷(HWI),可根據(jù)任務(wù)的優(yōu)先級和當(dāng)前執(zhí)行狀況調(diào)度或搶占任務(wù)。陀螺信號處理任務(wù)在數(shù)據(jù)采集任務(wù)的空閑周期執(zhí)行,也就是在采樣值寫入FIFO緩沖區(qū)這段時間執(zhí)行。當(dāng)數(shù)據(jù)采集任務(wù)執(zhí)行完成,發(fā)送旗語信號量SEM_PROC陀螺信號的處理任務(wù),對數(shù)據(jù)緩沖區(qū)內(nèi)的采樣值進行處理,如果沒有收到旗語信號量SEM_PROC任務(wù)自動掛起。

上位機通信任務(wù)負責(zé)系統(tǒng)與外部通信,將處理完成的數(shù)據(jù)通過SCI接口傳輸給上位機。上位機通信任務(wù)同樣采用DSP/BIOS中的TSK線程實現(xiàn)。上位機通信任務(wù)的優(yōu)先級低于任務(wù)陀螺信號處理任務(wù),在數(shù)據(jù)采集和信號處理的間隙執(zhí)行。陀螺信號處理任務(wù)執(zhí)行完成,發(fā)送旗語信號量SEM-XMIT上位機通信任務(wù),將數(shù)據(jù)送出。

3 MEMS信號處理平臺軟件設(shè)計方案

MEMS陀螺儀信號處理平臺的軟件設(shè)計包括DSP程序設(shè)計、FPGA控制和時序程序設(shè)計。DSP編程的主要任務(wù)是初始化、管理板上的資源,并實現(xiàn)前端數(shù)字信號處理的算法。這里以TI公司提供的功能強大的CCS(Code Composer Studio)為集成開發(fā)環(huán)境。

系統(tǒng)上電復(fù)位后。首先完成DSP自身的初始化,包括配置RAM模塊,設(shè)置I/O模式、定時器模式、中斷等,然后程序進人循環(huán)狀態(tài),等待中斷。

FPGA的軟件設(shè)計主要包括對A/D的采集控制、數(shù)據(jù)存儲與傳輸?shù)目刂啤⑿盘柕念A(yù)處理和同步時序的產(chǎn)生與控制。首先由FPGA把A/D采集來的MEMS陀螺儀的數(shù)據(jù)存儲在FPGA中,然后由FPGA對采集來的信號進行預(yù)處理,然后等待DSP的控制信號把預(yù)處理的信號送入DSP中進行信號處理和傳輸。系統(tǒng)軟件的設(shè)計方案如圖3所示。

4 結(jié) 語

本文設(shè)計的MEMS陀螺信號處理平臺,能夠完成三軸陀螺信號的采集和處理,并將處理過的MEMS陀螺信號發(fā)送給主機,由于采用了TI公司高性能的DSP芯片TMS320VC33,并在軟件設(shè)計中采用了DSP/BIOS多任務(wù)機制,使得該信號處理平臺具有體積小,精度高,實時性好等優(yōu)點,能夠滿足對MEMS陀螺信號處理,在實際應(yīng)用中具有一定的參考價值。

推薦閱讀: